Là một Nhà thiết kế PCB, bạn phải quản lý nhiều yêu cầu và kỳ vọng khác nhau. Có các khía cạnh về điện, chức năng và cơ khí cần xem xét. Ngoài ra, bố cục PCB phải được sản xuất một cách kịp thời, với chất lượng tốt nhất, chi phí thấp nhất có thể. Và qua tất cả những yêu cầu này, bạn cũng cần phải tính đến DFM (Thiết kế cho Khả năng Sản xuất). Đó là một phần quan trọng của quy trình thiết kế PCB và là một phần thường xuyên gây ra vấn đề nếu không được thực hiện đúng cách.

Vấn đề DFM phổ biến trong bố cục PCB của bạn

Việc tìm kiếm sự an toàn trong các công cụ CAD của bạn là dễ dàng, nhưng các công cụ CAD của bạn có thể cho phép bạn tạo ra các vấn đề DFM mà có thể không dễ dàng được giải quyết. Mặc dù bảng mạch của bạn vượt qua tất cả các kiểm tra quy tắc điện và là đúng về mặt điện, nó có thể không thể sản xuất được. Tại sao lại xảy ra điều này? Liệu công cụ thiết kế PCB của bạn không nên giúp bạn tạo ra một bố cục bảng mạch vừa có chức năng điện và có thể sản xuất hàng loạt?

Bố cục PCB của bạn có thể trở nên rất phức tạp và có thể ẩn giấu nhiều vấn đề DFM nếu bạn không biết phải chú ý đến những điểm nào. Một số vấn đề DFM này tạo ra các vấn đề với việc lắp ráp, kiểm tra điện, hoặc chế tạo, nhưng tất cả những vấn đề này có thể được khắc phục nếu bạn biết nhiều hơn về quy trình sản xuất. Nếu bạn đã sẵn sàng tìm hiểu thêm về những gì nhà sản xuất của bạn tìm kiếm trong quá trình đánh giá thiết kế, dưới đây là một số vấn đề DFM phổ biến nhất mà họ sẽ cố gắng phát hiện trong bất kỳ bố cục PCB nào:

- Kết nối Pad SMD không đều

- Mở Mặt Nạ Hàn không đúng trên Pad SMD

- Vias trong Pad SMD

- Bẫy Axit

- Khoảng cách

- Vi phạm Tiêu chuẩn Độ tin cậy thông thường

Ngăn chặn những vấn đề này có nghĩa là dựa vào các quy tắc thiết kế trong công cụ bố cục PCB của bạn, có thể giúp đảm bảo rằng bo mạch của bạn có thể được đưa vào sản xuất với thời gian đánh giá thiết kế tối thiểu.

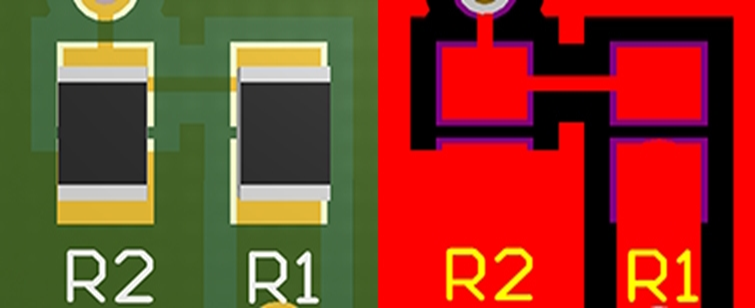

Kết nối pad SMD không đều

Các linh kiện SMD nhỏ, như 0402, 0201, v.v., cần phải có kết nối đồng đều để giúp ngăn chặn hiện tượng tombstoning trong quá trình hàn reflow. Điều này cũng áp dụng cho các pad BGA để đảm bảo hàn tin đáng tin cậy. Đơn giản chỉ là việc đặt kích thước pad phù hợp trên bản vẽ chân linh kiện của bạn. Các linh kiện phổ biến có kích thước pad được xác định (ví dụ, các pad trên IC theo tiêu chuẩn IPC-7351) mà bạn nên đặt trong bản vẽ chân linh kiện của mình.

.Bạn có thể kiểm tra kích thước pad dưới các linh kiện trong 3D mà không cần xuất file Gerber

Nhà sản xuất của bạn không phải lúc nào cũng xem xét các tệp thiết kế của bạn để kiểm tra điều này. Thay vào đó, họ có thể sẽ xem xét các tệp Gerber và netlist của bạn, và họ có thể so sánh các bản vẽ chân linh kiện với kích thước linh kiện trong danh sách vật liệu của bạn. Tùy thuộc vào mức độ dịch vụ kỹ thuật không lặp lại bạn yêu cầu, nhà sản xuất của bạn có thể không phát hiện ra khuyến nghị cụ thể này cho đến khi quá muộn. Sau khi sản xuất, quy trình kiểm tra để đảm bảo kết nối đều với pad bao gồm kiểm tra bằng X-ray. Trước khi bạn gửi thiết kế của mình đi sản xuất, bạn nên kiểm tra bất kỳ bản vẽ chân linh kiện footprint nào bạn thiết kế để đảm bảo chúng đúng với kích thước chân linh kiện.

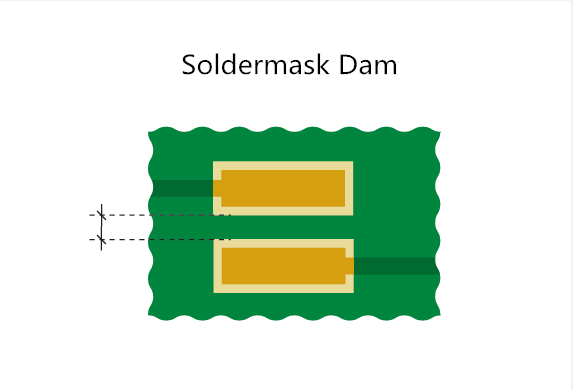

Sai kích thước mở mặt nạ hàn trên các pad SMD

Khoảng trống mặt nạ hàn (còn được gọi là sự mở rộng mặt nạ hàn hoặc khẩu độ mặt nạ hàn) là một cách để giữ chì hàn bị mắc kẹt trên pad mục tiêu trong quá trình hàn tay hoặc hàn sóng. Trong quá trình hàn, một viên chì hàn sẽ hình thành trên pad mục tiêu, nhưng một viên chì hàn lớn có thể sụp đổ và chảy quanh pad ở nhiệt độ cao. Đặt một khoảng trống mặt nạ hàn nhỏ xung quanh pad sẽ giữ viên chì hàn đó tại chỗ trong quá trình hàn, ngay cả khi viên chì hàn được đặt có kích thước hơi lớn. Một kỹ thuật tương tự được sử dụng trong việc fanout chân BGA kiểu dog-bone, nơi một lượng nhỏ mặt nạ hàn chặn pad khỏi via (gọi là solder dam).

Vấn đề này được giải quyết khi bạn tạo các footprint cho các linh kiện của mình, sẽ có một khoảng trống mặt nạ hàn xác định xung quanh pad. Nói chung, khoảng trống mặt nạ hàn sẽ mở rộng khoảng ~4 đến 5 mils ra ngoài mép của pad. Nếu độ mở mặt nạ hàn quá lớn, nó sẽ không ngăn chặn được dòng chảy và sự kết nối của viên chì hàn trong quá trình hàn sóng.

Mở Solder Mask xung quanh một via

Solder mask dam

Fanout via kiểu dog-bone cho chip BGA

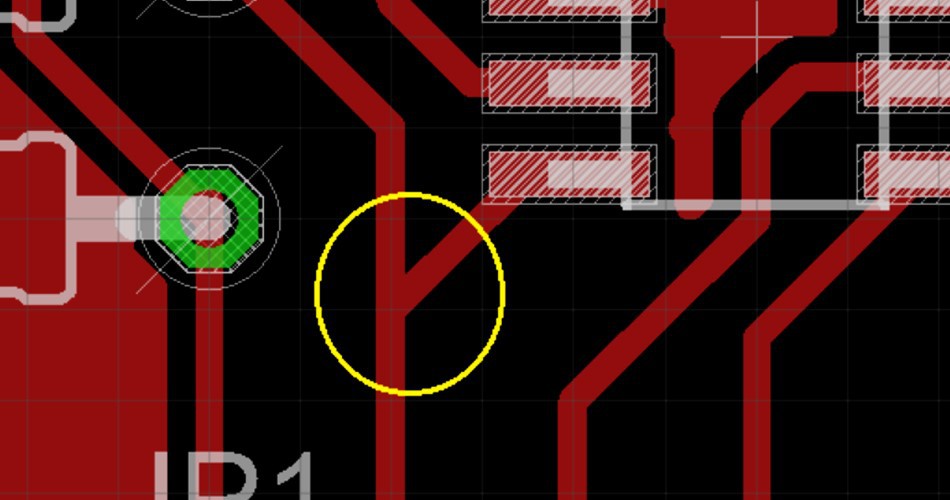

Vias trong các pad SMD

Đây là một lời khuyên thông thường trong thiết kế bảng mạch in mà bạn nên tránh việc sử dụng via-trong-pad bằng mọi giá. Nếu một via xuyên lỗ được đặt quá gần khu vực hàn, lỗ này có thể cho phép hàn chảy xuyên qua mặt sau của bảng mạch. Nếu via kết nối trực tiếp với một mặt phẳng lớn trong lớp trong inner, nhiệt độ sẽ tỏa ra vào mặt phẳng plane. Điều này có thể tạo ra một mối hàn mất nhiệt hoặc gây ra hiện tượng tombstoning trong quá trình hàn sóng.

Ví dụ Via trong Pad Có Thể Dẫn đến Mối Hàn Yếu

Via-trong-pad thực sự có một vị trí trong thiết kế PCB, đặc biệt là trong các thiết kế HDI với BGA có khoảng cách chân rất nhỏ. Trong các tình huống khác, khi muốn trace đến mặt phẳng plane đất được tối thiểu hóa, sử dụng một trace ngắn với lớp phủ hàn hoặc via được phủ. Để ngăn chặn sự tỏa nhiệt quá mức vào lớp mặt phẳng trong quá trình hàn, đặt một via giảm nhiệt vào kết nối với mặt phẳng.

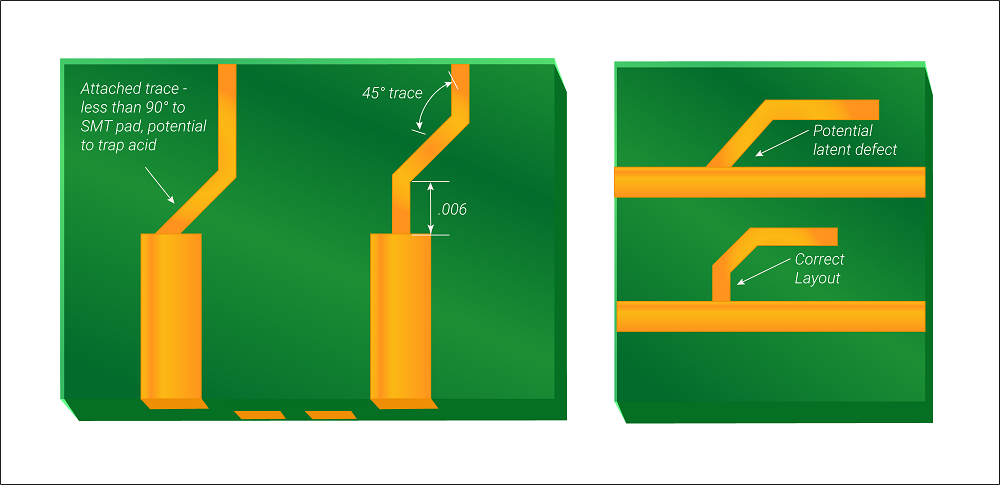

Bẫy Axit

Quy trình tạo ảnh đồng trên từng lớp bảng mạch in (PCB) phụ thuộc vào nhiều yếu tố. Đồng được loại bỏ khỏi vật liệu lớp phủ bằng dung dịch ăn mòn kiềm, cơ bản là phản ứng với đồng và từ từ hòa tan nó. Các đặc điểm đồng trong PCB của bạn với các góc chặt có thể cho phép dung dịch ăn mòn đặc bị mắc kẹt, được biết đến như một bẫy axit, làm ăn mòn quá mức đồng gần đó. Điều này dẫn đến độ nhám đồng quá mức tại vị trí bẫy axit.

Các trace được định tuyến với góc 45 độ để tránh bẫy ăn mòn

Lưu ý rằng vấn đề về bẫy axit đã được giải quyết phần nào thông qua việc sử dụng dung dịch ăn mòn độ nhớt thấp. Nếu bạn dự định đi dây ở góc 90 độ hoặc các góc tù khác, hãy chắc chắn kiểm tra loại dung dịch ăn mòn mà nhà sản xuất sử dụng và liệu nó có gây ra bẫy axit hay không.

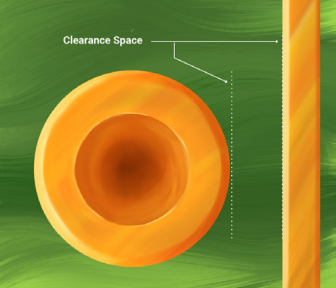

Khoảng cách (Clearance)

Việc duy trì khoảng cách phù hợp là một khía cạnh cơ bản của thiết kế PCB, nhưng công cụ định tuyến của bạn sẽ cho phép bạn xác định hầu như bất kỳ khoảng cách nào nếu bạn không thiết lập các luật thiết kế chính xác. Các trace cần được giữ cách xa các pad, các trace khác và đổ đồng để cho phép ăn mòn hoàn toàn và tạo ra không gian cho dung sai sản xuất.

Lý do khác để duy trì khoảng cách phù hợp xuất phát từ thiết kế điện áp cao. Dưới Tiêu chuẩn IPC 2221, khoảng cách tối thiểu giữa một trace và bất kỳ thành phần dẫn điện nào khác phụ thuộc vào sự chênh lệch điện thế trung bình giữa các vật dẫn điện này. Mục tiêu ở đây là để ngăn chặn việc phóng điện không mong muốn, sự hình thành sợi anodic dẫn điện cho các dẫn điện gần nhau, và sự ăn mòn điện hóa.

Vi phạm tiêu chuẩn độ tin cậy thông thường

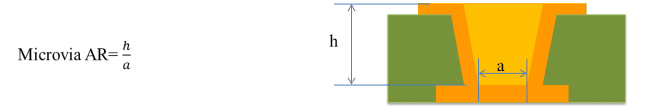

Có một danh sách dài các tiêu chuẩn IPC được thiết kế để đảm bảo độ tin cậy. Những tiêu chuẩn này bao gồm mọi thứ từ kích thước vòng annular của via đến tỷ lệ khía cạnh, và mọi thứ ở giữa. Một số yêu cầu độ tin cậy phổ biến được nêu trong các tiêu chuẩn IPC liên quan đến:

- Teardrops trên pad và via

- Kích thước Annular ring

- Kích thước và tỷ lệ aspect ratio(AR) của via/microvia

- Kích thước pad

- Độ rộng trace tương ứng với dòng điện và sự tăng nhiệt độ

Nhà sản xuất có thể kiểm tra trong Gerbers hoặc file thiết kế của bạn, cũng như trong yêu cầu kiểm tra của bạn, để xác định bạn có thể đã vi phạm tiêu chuẩn nào một cách không chủ ý. Hãy nhớ rằng các tiêu chuẩn IPC là tự nguyện (trừ trong các ngành công nghiệp được quy định nghiêm ngặt), nhưng bạn vẫn nên thiết kế theo các tiêu chuẩn này vì chúng đã chứng minh bản thân là cơ sở cho độ tin cậy của PCB.