“The Right Way to Use LC Filters on Microcontroller Analog Interfaces”. Video này từ Altium Academy, do Zach Peterson hướng dẫn, giải thích cách sử dụng bộ lọc LC để cách ly và lọc nhiễu cho giao diện analog của vi điều khiển (như chân VDDA). Dưới đây là nội dung chi tiết:

1. Giới thiệu và bối cảnh

-

Video thảo luận về một thực hành phổ biến: sử dụng bộ lọc LC để tách biệt đường nguồn analog (analog rail) khỏi đường nguồn kỹ thuật số (digital rail) khi cả hai dùng chung một nguồn cấp

-

Mục tiêu là lọc bỏ nhiễu từ các hoạt động chuyển mạch kỹ thuật số trước khi nó đi vào các chân analog nhạy cảm

2. Ví dụ thực tế từ các thiết kế tham khảo

-

Zach đưa ra ví dụ từ các thiết kế sử dụng vi điều khiển STM32. Trong đó, đường nguồn 3.3V chính đi qua một bộ lọc LC (gồm cuộn cảm và tụ điện) trước khi cấp vào chân VREF hoặc VDDA

-

Mặc dù bảng dữ liệu (datasheet) của STM32 thường chỉ yêu cầu các tụ decoupling riêng biệt cho VDD và VDDA, nhiều thiết kế thực tế và diễn đàn kỹ thuật (như TI E2E) khuyên dùng thêm cuộn cảm để tăng hiệu quả lọc nhiễu

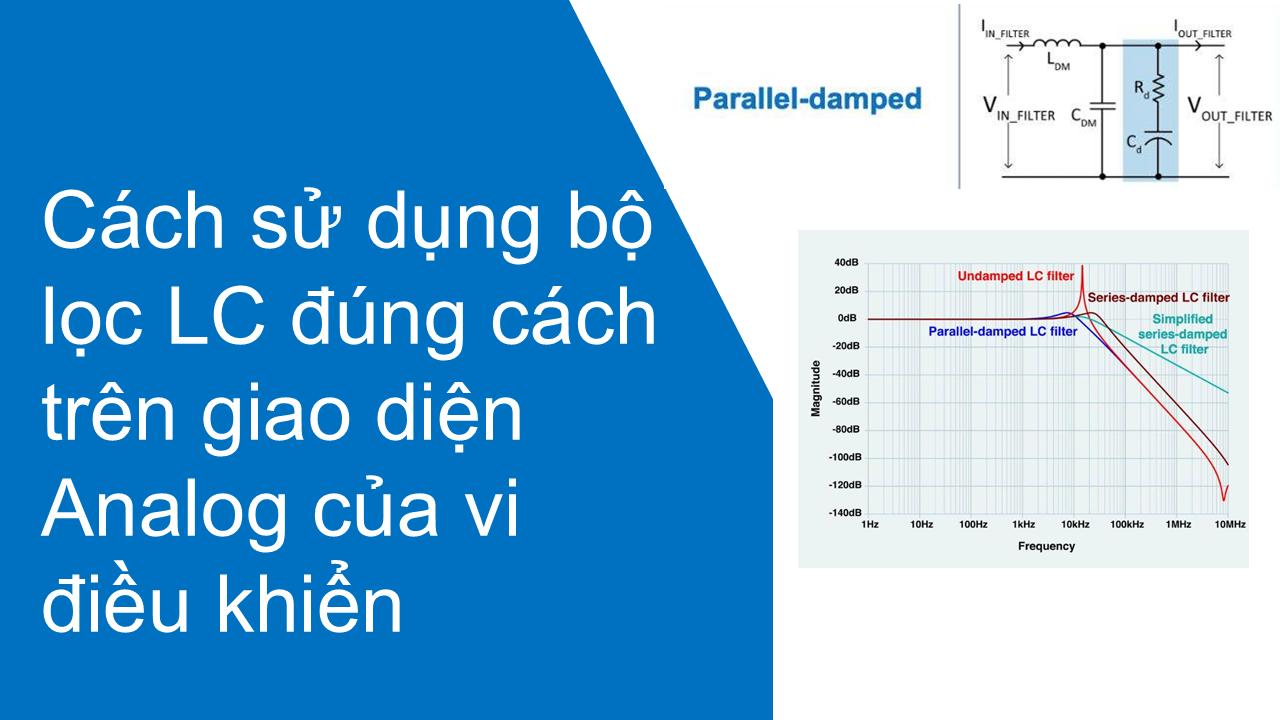

3. So sánh bộ lọc LC và Ferrite Bead

-

Ferrite Bead: Thường dùng để nhắm vào nhiễu tần số cao. Tuy nhiên, nó có đặc tính trở thành tụ điện ở tần số rất cao, làm giảm khả năng chặn nhiễu

-

Bộ lọc LC: Hoạt động như một bộ lọc thông thấp (low-pass filter) ổn định hơn cho đến dải tần số GHz. Nó có thể nhắm vào các tần số thấp hơn (ví dụ: 150 kHz) so với Ferrite Bead

4. Kết quả mô phỏng trên Altium Designer

Zach thực hiện mô phỏng để kiểm tra hiệu quả của bộ lọc LC với các nguồn nhiễu khác nhau:

-

Hiện tượng cộng hưởng (Resonance): Bộ lọc LC có một đỉnh cộng hưởng tại một tần số nhất định (trong ví dụ là khoảng 158 kHz). Nếu nhiễu từ nguồn cấp trùng với tần số này, nhiễu sẽ bị khuếch đại lên gấp 2-3 lần thay vì bị giảm đi

-

Hiệu quả lọc nhiễu:

-

Khi nhiễu nguồn (từ bộ điều áp xung) ở mức 400 kHz (cao hơn tần số cắt 150 kHz), bộ lọc hoạt động rất tốt, giảm khoảng 67% biên độ nhiễu

-

Khi nhiễu ở mức 80 kHz (thấp hơn tần số cắt), nhiễu hầu như đi qua bộ lọc mà không bị suy giảm

-

5. Những lưu ý quan trọng khi thiết kế

-

Chọn kích thước bộ lọc phù hợp: Bạn phải biết tần số nhiễu của nguồn cấp (ví dụ: tần số chuyển mạch của Buck converter) để thiết kế tần số cắt của bộ lọc LC thấp hơn mức đó

-

Tránh cản trở nguồn cấp cho ADC: Tần số hoạt động của bộ chuyển đổi Analog-to-Digital (ADC) phải thấp hơn tần số cắt của bộ lọc để đảm bảo mạch analog vẫn có thể rút điện năng cần thiết mà không bị bộ lọc chặn lại

-

Dập tắt cộng hưởng (Damping): Có thể sử dụng các linh kiện có nội trở ESR cao hoặc thêm điện trở nhỏ nối tiếp để giảm đỉnh cộng hưởng, nhưng cần thận trọng vì nó có thể gây sụt áp

Kết luận

Bộ lọc LC là công cụ mạnh mẽ để bảo vệ tín hiệu analog, nhưng nếu thiết kế sai tần số, nó có thể làm trầm trọng thêm vấn đề nhiễu do hiện tượng cộng hưởng. Người thiết kế cần hiểu rõ nguồn nhiễu và dải tần hoạt động của mạch để áp dụng đúng cách.

http://www.youtube.com/watch?v=mSehCGvPXOI