Nguyên tắc thiết kế EMC

Các hướng dẫn thiết kế Tương thích Điện từ (EMC) này ở đây để giúp bạn hiểu những kiến thức cơ bản về cách tạo ra một thiết kế PCB EMC tốt hoặc thiết kế cáp EMC. Tốt ở trong bối cảnh này có nghĩa là: với Nhiễu điện từ (EMI) thấp.

Việc tuân theo các hướng dẫn này đã giúp nhiều kỹ sư thành công trong thử nghiệm EMC của một số sản phẩm. Tuy nhiên, hãy lưu ý rằng chỉ các hướng dẫn không thể làm nên những điều kỳ diệu cho thiết kế của bạn. Hãy cảnh giác! Tuy nhiên, hiểu đúng những điều cơ bản sẽ giảm bớt khó khăn khi kiểm tra EMC và tăng cơ hội PASS đến đúng với lần đầu tiên. Và đó là tất cả những gì chúng ta muốn, phải không?

Mục lục

Lời nói đầu cho các nguyên tắc:

- Lời nói đầu – Mặt phẳng plane GND và mặt phẳng tham chiếu trả về tín hiệu.

Hướng dẫn thiết kế EMC cơ bản cho thiết kế PCB :

- Hướng dẫn số 1 – Không bao giờ định tuyến tín hiệu qua các mặt phẳng tham chiếu phân chia!

- Nguyên tắc # 2 – Giữ các vòng lặp dòng điện càng nhỏ càng tốt.

- Hướng dẫn # 3 – Decoupling: sử dụng tụ điện/trace/plane có độ tự cảm thấp.

- Hướng dẫn # 4 – Sử dụng ground plane trên PCB để che chắn.

- Hướng dẫn # 5 – Định tuyến các tín hiệu tần số cao được điều chỉnh đến một mặt phẳng plane.

- Nguyên tắc số 6 – Kiểm soát thời gian tăng và giảm – rise time & fall time.

- Hướng dẫn # 7 – Thêm tụ gốm gần mỗi chân của connector.

- Hướng dẫn # 8 – Điền đầy lớp trên và dưới bằng mạch GND và làm mờ các cạnh PCB.

- Hướng dẫn # 9 – Thêm via stitching xung quanh via tín hiệu tốc độ cao.

- Hướng dẫn # 10 – Kết nối mạch GND với vỏ chassis tại khu vực IO.

Hướng dẫn thiết kế EMC cơ bản cho hệ thống cáp và hệ thống dây điện:

- Hướng dẫn # 11 – Đặt cáp dọc theo vỏ chassis (GND / đất).

- Hướng dẫn # 12 – KHÔNG sử dụng vỏ cable (cable shield) làm dây dẫn tín hiệu cho các tín hiệu tần số thấp.

- Hướng dẫn # 13 – Chỉ đặt một đầu của vỏ cable (cable shield) cáp tiếp đất đối với tín hiệu tần số thấp.

- Hướng dẫn # 14 – Đặt cả hai đầu của vỏ cable (cable shield) cáp xuống đất để nhận tín hiệu tần số cao.

- Hướng dẫn # 15 – Giảm thiểu diện tích vòng lặp của tín hiệu trong cáp.

Lời nói đầu

Chúng tôi cố gắng tránh các thuật ngữ ground plane và GND plane trong hướng dẫn của chúng tôi. Bất cứ khi nào thích hợp, chúng tôi sử dụng thuật ngữ mặt phẳng trả về tín hiệu hoặc mặt phẳng tham chiếu tín hiệu trở về hoặc đơn giản là: mặt phẳng plane tham chiếu reference plane. Tại sao lại thê này?

Dòng điện chạy theo vòng kín – loop. Dòng điện luôn luôn quay trở lại nguồn của nó.

Và một vấn đề phổ biến là các kỹ sư có xu hướng quên điều này khi họ thiết kế PCB và các hệ thống điện tử, đặc biệt là khi họ thiết kế các hệ thống số nơi bạn chỉ có thể nhìn thấy các trace tín hiệu từ chip này sang chip khác và dòng điện trở về chạy qua các “ký hiệu GND – GND symbol ” trong mạch nguyên lý schematic. Phần lớn các vấn đề về EMC (ví dụ như phát xạ bức xạ, ESD) liên quan đến tín hiệu tần số cao (vài megahertz – MHz). Điều quan trọng là phải hiểu rằng dòng điện trở về của tín hiệu trên khoảng 50kHz luôn đi bên dưới với dòng điện theo chiều đi, ví dụ trực tiếp dưới dòng điện theo chiều đi trong ground plane – cái gọi là mặt phẳng tham chiếu tín hiệu trở về .

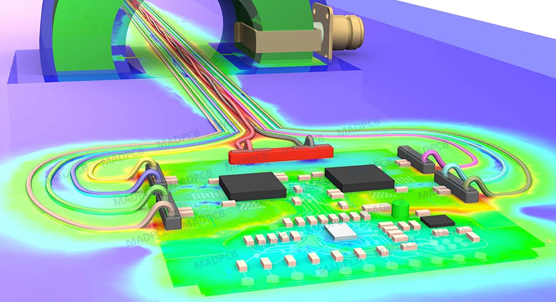

Hai hình ảnh ấn tượng sau đây so sánh dòng điện trở về thông qua mặt phẳng tham chiếu của tín hiệu tần số thấp và tín hiệu tần số cao (nguồn: EMI Troubleshooting Cookbook for Product Designers). Trong hình bên trái, tín hiệu có tần số 1kHz và ở bên phải là 1MHz. Sự khác biệt là rõ ràng và đã mở rộng tầm mắt! Vì vậy, hãy bắt đầu với các nguyên tắc và tìm hiểu thêm về thiết kế tuân thủ EMC.

Thiết kế PCB

Hướng dẫn EMC # 1 – Không bao giờ định tuyến tín hiệu qua các mặt phẳng plane tham chiếu bị chia cắt – split reference plane

Hình ảnh: TI http://www.ti.com/

Giảm phát xạ bức xạ

Không định tuyến tín hiệu qua các mặt phẳng tham chiếu tín hiệu trả về bị chia cắt (GND, mặt phẳng plane nguồn)! Không bao giờ! Điều này dẫn đến các vòng dòng điện lớn không cần thiết (vì dòng điện quay trở về không thể chạy trực tiếp bên dưới / bên cạnh dòng điện theo chiều đi) và các vòng dòng điện lớn nói chung dẫn đến các giá trị phát bức xạ cao.

Quy tắc Ngón tay cái # 1 : Bất cứ khi nào nghi ngờ, không chia cắt các mặt phẳng tham chiếu cho dòng điện trở về (GND, mặt phẳng plane nguồn), thay vào đó hãy sử dụng một mặt phẳng tham chiếu được điền đầy(solid). Phải có một lý do chính đáng cho việc tách/chia cắt plane! Luôn phải có ít nhất một mặt phẳng tham chiếu solid được điều chỉnh chặt chẽ để phù hợp với các tín hiệu.

Hướng dẫn EMC # 2 – Giữ các vòng lặp dòng điện càng nhỏ càng tốt.

Giảm phát xạ bức xạ

Luôn luôn xem xét đường trở về của dòng điện! Luôn luôn! Và lưu ý đến dòng điện trở về: giảm thiểu vòng lặp bạn có giữa dòng điện theo chiều đi và dòng điện trở về. Điều này đặc biệt đúng đối với tín hiệu tần số cao (vài MHz), nói cách khác: Tín hiệu Clock! Như Henry W. Ott đã nói: “Hãy hoang tưởng về Clock!”.

Đây là một hướng dẫn rất chung chung và cần luôn được ghi nhớ. Ngoài hướng dẫn này, nhiều người khác sẽ làm theo hướng dẫn ở đây một cách cụ thể hơn.

Gợi ý # 1 : Chúng tôi giả định rằng bạn có trace tín hiệu tần số cao (s1 ,> 1MHz) trên lớp 1 và mặt phẳng tham chiếu (ví dụ: GND hoặc mặt phẳng plane nguồn) trên lớp 2 liền kề, dòng điện trở về của mức cao tín hiệu tần số (s1) trên mặt phẳng tham chiếu luôn có xu hướng truyền trực tiếp bên dưới trace của s1. Đọc thêm chi tiết trong cuốn sách này tại đây hoặc lời nói đầu của các hướng dẫn này.

Hướng dẫn EMC # 3 – Decoupling: sử dụng tụ điện/trace/plane có độ tự cảm thấp

Giảm phát xạ bức xạ, giảm ghép nối trở kháng

Decoupling là quan trọng! Luôn xem xét việc Decoupling! Đặt các tụ gốm gần MỌI chân cấp nguồn của MỌI chip trên thiết kế PCB của bạn.

Gợi ý # 2:

Decoupling tùy thuộc vào stackup của PCB:

- PCB nhiều lớp: Thiết kế một stackup PCB với mặt phẳng cấp nguồn và mặt phẳng GND gần nhau (<0.1 mm hoặc 2 … 3 mil). Điều này dẫn đến việc decoupling đặc biệt tốt ở tần số cao (> 1MHz).

- PCB hai lớp/ một lớp: Giữ trace của các tụ điện decoupling đến chân cấp nguồn và chân GND càng ngắn càng tốt (để giữ điện cảm càng thấp càng tốt).

Hướng dẫn EMC # 4 – Sử dụng ground plane trên PCB để che chắn – shielding.

Giảm nhiễu trên mạch PCB

Sử dụng các mặt phẳng tham chiếu liên tục/solid (ví dụ GND hoặc mặt phẳng plane nguồn) trên PCB để tách các tín hiệu nhiễu (ví dụ: tín hiệu động cơ) khỏi các tín hiệu nhạy cảm (ví dụ: tín hiệu cảm biến). Mặt phẳng tham chiếu sẽ hoạt động như một lá chắn và sẽ làm giảm nhiễu điện từ (EMI). Cần biết rằng việc che chắn mặt phẳng đồng – copper plane như vậy sẽ chủ yếu có hiệu quả đối với điện trường E chứ không phải từ trường H, vì đồng có độ từ thẩm μr thấp và không che chắn chống lại từ trường (tần số thấp). Đọc thêm về che chắn trong Knowledge Database của chúng tôi.

Hướng dẫn EMC # 5 – Định tuyến các tín hiệu tần số cao được điều chỉnh đến một mặt phẳng.

Giảm phát xạ bức xạ

Hướng dẫn này tuân theo Hướng dẫn EMC # 1 và Hướng dẫn EMC # 2 : định tuyến tín hiệu tần số cao (> 50kHz) LUÔN LUÔN gần với mặt phẳng tham chiếu đã điều chỉnh (GND hoặc mặt phẳng plane nguồn, hoạt động trong trường hợp này là ground plane tần số cao). Đối với thiết kế PCB một lớp: sử dụng các trace bảo vệ gần với tín hiệu tần số cao nơi dòng điện trở về có thể chạy qua.

Gợi ý # 3: Nói chung, lõi laminate dễ tái tạo hơn so với prereg liên quan đến độ dày và hằng số điện môi. Điều này có nghĩa là lý tưởng nhất là các lớp trở kháng được kiểm soát nên được định tuyến dọc theo vật liệu lõi, thay vì prereg. Đọc thêm về stackup các lớp PCB trong Knowledge Database của chúng tôi .

Hướng dẫn EMC # 6 – Kiểm soát thời gian tăng và giảm – rise time và fall time.

Giảm phát xạ bức xạ

Tăng thời gian tăng và giảm của bất kỳ tín hiệu số nào (đặc biệt là tín hiệu clock) càng xa càng tốt.

Quy tắc Ngón tay cái #2 : Thêm một điện trở nối tiếp (thường là 33 Ohm, gần với đầu ra của bên truyền/driver) vào tất cả các trace tín hiệu số có độ dài tín hiệu [inch] cao hơn thời gian tăng/giảm [ns].

Quy tắc Ngón tay cái #3: Nội dung tần số gần đúng trong tín hiệu số KHÔNG phụ thuộc vào sóng hài đầu tiên (tần số cơ bản), nó phụ thuộc vào thời gian tăng/giảm:

Trong đó t10% -90% là thời gian tăng hoặc giảm từ 10% đến 90% độ dốc của tín hiệu số tính bằng [giây] và f knee là nội dung tần số tối đa tính bằng [Hz].

Ví dụ: Cho một tín hiệu clock có thời gian tăng/giảm t 10% -90% = 1ns chạy trên một trace microstrip PCB có chiều dài 250mm (10 inch). Nội dung tần số cao nhất trong tín hiệu số này xấp xỉ f max = f knee ≈350MHz và có bước sóng λ ≈ v / f knee = 500mm, trong đó v là vận tốc lan truyền của sóng điện từ bên trong tín hiệu PCB và không khí (điển hình hằng số điện môi εr = 4,5 đối với FR-4 và hằng số điện môi hiệu dụng ε reff ≈3,0 đối với đường microstrip giả định):

Tín hiệu clock với thời gian tăng/giảm 1 giây chạy qua một trace trên PCB với vật liệu FR-4 cho kết quả là λ/2 = 250mm và λ/10 = 50mm đối với f max . Với tất cả những thực tế này, trace PCB có chiều dài 250mm sẽ có xu hướng bức xạ ở mức cao (vì chiều dài trace hoặc cáp có chiều dài λ/2 tạo nên một ăng-ten tốt). Để ngăn chặn điều này: thêm một điện trở nối tiếp gần với đầu ra của bên truyền/driver sẽ làm giảm thời gian tăng/giảm.

Quy tắc Ngón tay cái #4: Mọi trace PCB có chiều dài hơn λ/10 nên được coi là một đường truyền transmission line và không còn là một kết nối đơn giản nữa. Điều này có nghĩa là một trace như vậy nên được xác định với trở kháng được kiểm soát. Nói cách khác: không được có bất kỳ thay đổi/gián đoạn trở kháng nào dọc theo trace PCB, vì những thay đổ /gián đoạn trở kháng này dẫn đến phản xạ. Phản xạ ảnh hưởng đến tính toàn vẹn của tín hiệu (không phải là chủ đề ở đây) và dẫn đến bức xạ điện từ. Đọc thêm chi tiết trong cuốn sách này ở đây .

Hướng dẫn EMC # 7 – Thêm tụ gốm ceramic gần mỗi chân của connector.

ESD, giảm phát xạ bức xạ, tăng khả năng miễn nhiễm bức xạ

Việc lọc tín hiệu trực tiếp tại connector là rất quan trọng! Điều này giúp bổ sung khả năng miễn dịch Xả tĩnh điện (ESD) cho PCB của bạn, giảm phát xạ bức xạ và tăng khả năng miễn nhiễm với các tín hiệu/nhiễu quá điện áp được ghép nối trên cáp IO.

Mọi tín hiệu hoặc đường cung cấp điện đi vào hoặc rời khỏi PCB của bạn đều cần một tụ điện gốm. Một bên của tụ điện đóng vào chân connector, chân còn lại nối đến mặt phẳng đất GND. Một số quy tắc ngón tay cái:

Gợi ý # 4: Các tín hiệu đi ra bên ngoài thiết bị của bạn (ví dụ: connector mà mọi người có thể chạm vào bằng tay), sẽ được kiểm tra bằng súng ESD (± 2kV, ± 4kV, ± 6kV, ± 8kV). Trong trường hợp này, sử dụng tụ điện có định mức điện áp cao (ví dụ> 250V, tùy thuộc vào điện dung và điện áp thử nghiệm ESD và các linh kiện khác liên quan, ví dụ như hạt ferrite bead giữa chân connector và tụ điện).

Hướng dẫn EMC # 8 – Điền đầy các lớp trên và dưới (Top và Bottom) với GND và kim loại hóa các cạnh PCB.

Giảm phát xạ

Đổ đầy các lớp trên cùng và dưới cùng của PCB bằng một mặt phẳng đất solid xung quanh các tín hiệu (khu vực đồng) và kim loại hóa các cạnh PCB. Điều này giúp giảm thiểu phát xạ bức xạ, vì các khu vực GND được lấp đầy ở trên cùng và dưới cùng của PCB giúp che chắn các tín hiệu lớp bên trong khỏi bức xạ. Hơn nữa, các khu vực đồng được lấp đầy giúp duy trì một đường dẫn dòng điện trở về trở kháng thấp và do đó các vòng lặp dòng điện ngắn. Tuy nhiên, đừng quên đặt một lưới via stitching nối đất trên toàn bộ PCB (nếu không một số vùng đồng nhỏ có thể phát xạ)! Cái này rất quan trọng! Đọc về khoảng cách giữa các via bên dưới trong Quy tắc ngón tay cái # 5.

Các cạnh bên ngoài PCB được mạ (được kết nối với mạch GND) giúp ngăn các lớp PCB bên trong bức xạ. Hơn nữa, các cạnh PCB được mạ giúp tăng hiệu quả làm mát của PCB, vì có thêm một bề mặt đồng để trao đổi nhiệt có thể diễn ra. Chi phí bổ sung cho các cạnh PCB được kim loại hóa là thấp.

Quy tắc ngón tay cái # 5 : Cách tốt nhất là thêm một lưới các via stitching nối đất trên toàn bộ PCB (khi lấp đầy các lớp trên cùng và dưới cùng bằng một mặt phẳng plane đất). Nếu không, một số khu vực đồng GND nhỏ sẽ có xu hướng phát xạ! Khoảng cách giữa các via này trong lưới đó phụ thuộc vào tần số f max cao nhất trên PCB. Với một tín hiệu có bước sóng λ, quy luật chung là một trace hoặc trace có độ dài λ/ 10 bắt đầu trở thành vấn đề (liên quan đến bức xạ) và trace có độ dài λ/20 sẽ không thành vấn đề (trong giữa λ / 10 và λ/20 là một vùng xám). Do đó, khoảng cách giữa các vias phải ngắn hơn λ/ 10 của f max . Bước sóng λ của tín hiệu hình sin chạy qua trace tín hiệu PCB là (đọc công thức này trong chương của chúng tôi về Frequency and Wavelength ):

Trong đó λ = bước sóng [m], c = tốc độ ánh sáng [3E8 m / giây], f = tần số [Hz] và ε r = độ thẩm thấu [1] của vật liệu PCB (ví dụ ε r = 4,5 điển hình cho FR-4 và ví dụ: ε r = 2 … 11 đối với vật liệu PCB tần số cao đặc biệt (f > 2GHz), trong đó cần hằng số điện môi đẳng hướng và ổn định trên dải tần rộng, dải nhiệt độ và mọi lô PCB).

Nhưng làm thế nào để xác định f knee = f max hoặc λ / 10, tương ứng? Thông thường, tần số cao nhất xảy ra trong các tín hiệu số với thời gian tăng / giảm nhỏ, đặc biệt là tín hiệu clock. Một ước tính tốt đưa ra Quy tắc Ngón tay cái # 3 của chúng tôi với:

Bảng sau đây cho thấy một số giá trị ví dụ về thời gian tăng / giảm tín hiệu số tần số cao và nội dung tần số cao nhất tương ứng của nó và các giá trị λ/10 (khoảng cách được khuyến nghị giữa các via của lưới via là < λ / 10).

Hướng dẫn EMC # 9 – Thêm via stitching xung quanh via tín hiệu tốc độ cao.

Giảm phát xạ bức xạ

Hướng dẫn này trực tiếp tuân theo Hướng dẫn số 2 của EMC. Hãy tưởng tượng tình huống sau: một tín hiệu tốc độ cao chuyển các mặt phẳng trên PCB. Để giảm thiểu hiện tượng dội lại ground bounce trên ground plane, bạn phải giảm thiểu đường dẫn dòng điện trở về. Có hai tùy chọn này, tùy thuộc vào đường dẫn dòng điện trở về:

- Các mạng lưới tham chiếu dòng trở lại giống hệt nhau. Trong trường hợp hai mặt phẳng có cùng lưới tham chiếu với điện thế giống hệt nhau (ví dụ GND), hãy thêm hai hoặc ba stitching via (giữa các mặt phẳng tham chiếu) gần với tín hiệu tốc độ cao qua. Các stitching via này giúp giữ các vòng kín dòng điện càng nhỏ càng tốt.

- Các mạng lưới tham chiếu tham chiếu dòng điện trở về khác nhau. Trong trường hợp hai mặt phẳng tham chiếu được cách ly DC, hãy đảm bảo rằng hai mặt phẳng tham chiếu được ghép với trở kháng thấp nhất có thể. Điều này có thể đạt được với lớp điện môi mỏng nhất có thể giữa chúng (xem hình bên dưới)

Hướng dẫn EMC # 10 – Kết nối mạch GND với vỏ chassis tại khu vực IO.

Giảm phát xạ bức xạ, miễn nhiễm dẫn, ESD

Đừng nghĩ rằng hướng dẫn này không quan trọng, chỉ vì nó không được liệt kê ngay từ đầu! Hướng dẫn này là rất cần thiết! Gắn GND mạch của bạn vào vỏ chassis tại khu vực cáp của bạn rời/đi vào vỏ. Kết nối nó với trở kháng RẤT THẤP!

Điều quan trọng là GND và vỏ chassis có cùng điện thế tại khu vực IO:

- Điều này ngăn cản bức xạ, vì GND cho thấy sự chênh lệch điện áp tối thiểu với vỏ chassis (đất).

- Điều này giúp bộ lọc tín hiệu IO trên PCB của bạn (xem Hướng dẫn EMC # 7 ) hoạt động hiệu quả nhất và giữ các xung ESD cách xa mạch của bạn. Tại sao? Bởi vì nhiễu đến (quá điện áp, ESD) từ cáp có thể trực tiếp truyền ngược lại vỏ chassis xuống đất.

Thiết kế cáp & dây điện

Hướng dẫn EMC # 11 – Đặt cáp dọc theo vỏ chassis (GND / đất).

Phát xạ bức xạ thấp hơn, miễn nhiễm dẫn, ESD

Bất cứ khi nào có thể, hãy đặt dây cáp dọc theo vỏ chassis:

- Phát xạ: Điều này giữ cho trường điện từ được tạo ra bởi điện áp và dòng điện trong cáp ở mức bức xạ tối thiểu.

- Miễn dịch: Điều này giảm thiểu dòng điện cảm ứng trong cáp và vỏ cable (cable shield) cáp (giả sử rằng vỏ cable (cable shield) được đặt ở cả hai connector đất). Lý do: diện tích vòng lặp cho dòng điện cảm ứng được giảm thiểu.

Hướng dẫn EMC # 12 – KHÔNG sử dụng vỏ cable (cable shield)/vỏ bọc/ shield làm dây dẫn tín hiệu cho các tín hiệu tần số thấp.

Tăng khả năng miễn dịch

Vỏ cable (cable shield) không nên là một trong những chất dẫn tín hiệu cho các tín hiệu tần số thấp (ví dụ: tín hiệu cảm biến)! Không bao giờ! Vì dòng điện nhiễu gây ra trong vòng nối đất – ground loop.

Gợi ý # 5: Quy tắc này KHÔNG áp dụng cho các tín hiệu tần số cao (!), Trong đó dòng điện trở về của tín hiệu và dòng nhiễu được phân tách bằng hiệu ứng da bên trong vỏ cable (cable shield) (ví dụ như trong cáp đồng trục). Xem Hướng dẫn # 14 .

Hướng dẫn EMC # 13 – Chỉ đặt một đầu của vỏ cable (cable shield) cáp tiếp đất đối với tín hiệu tần số thấp.

Tăng khả năng miễn nhiễm điện trường

Khi che chắn cáp, thường có câu hỏi này: “Chúng ta nên nối đất cho vỏ cable (cable shield) cáp ở cả hai đầu hay chỉ ở một đầu?” Có thể dẫn đến sự cố khi đặt cả hai đầu của vỏ cable (cable shield) cáp xuống đất cho tín hiệu tần số thấp, vì dòng điện cân bằng trong vỏ cable (cable shield) có thể dẫn đến nhiễu tín hiệu bên trong cáp. Dưới đây là quy tắc chung cho tín hiệu tần số thấp (<20kHz), tìm thêm chi tiết tại đây :

- Bảo vệ chống lại điện trường (E): chỉ đặt một đầu của vỏ cable (cable shield) xuống đất (có trở kháng thấp) để tránh dòng điện nhiễu qua vỏ cable (cable shield) (ví dụ như do từ trường hoặc dòng điện nối đất gây ra).

- Bảo vệ chống lại từ trường (H): tuân theo Hướng dẫn số 15 .

Nếu bạn chỉ kiểm soát một bên của vỏ cable (cable shield) cáp (vì ở đầu kia của cáp là thiết bị của nhà sản xuất khác): đặt vỏ cable (cable shield) cáp xuống đất/vỏ chassis có độ tự cảm thấp (sử dụng kẹp vỏ cable (cable shield) 360º) hoặc thực hiện Gợi ý # 6, nhưng ĐỪNG BAO GIỜ để nó không kết nối!

Gợi ý # 6: Một giải pháp tốt để che chắn đồng thời chống lại các tín hiệu tần số thấp và tần số cao, đồng thời giảm thiểu dòng điện cân bằng tần số thấp:

- Đặt một mặt của vỏ cable (cable shield) cáp xuống đất có điện cảm thấp và điện trở thấp.

- Đặt mặt kia của vỏ cable (cable shield) cáp xuống đất với một điện trở (để giảm thiểu dòng điện cân bằng đối với tín hiệu tần số thấp) và một tụ điện song song với điện trở đó (để cho phép tín hiệu tần số cao đi qua vỏ cable (cable shield) cáp).

Hướng dẫn EMC # 14 – Đặt cả hai đầu của vỏ cable (cable shield) cáp xuống đất để nhận tín hiệu tần số cao.

Tăng khả năng miễn nhiễm trường điện từ, giảm phát xạ từ trường

Khi che chắn cáp, thường có câu hỏi này: “Chúng ta nên nối đất cho vỏ cable (cable shield) cáp ở cả hai đầu hay chỉ ở một đầu?” Bắt buộc phải đặt cả hai đầu của vỏ cable (cable shield) cáp tín hiệu tần số cao xuống đất có điện cảm thấp (không có bím, sử dụng kẹp che chắn 360º hoặc tương tự). Đây là quy tắc của ngón tay cái cho tần số cao (> 1MHz) tín hiệu, tìm thêm chi tiết ở đây:

- Vỏ cable (cable shield) có thể được sử dụng làm đường trở lại tín hiệu cho tín hiệu tần số cao (vì dòng điện trở về tín hiệu và dòng điện nhiễu được phân tách bởi hiệu ứng skin (ví dụ: trong cáp đồng trục, bạn có thể tìm thấy độ sâu skin-depth được tính toán bên dưới). dòng nhiễu trong vỏ cable (cable shield) giúp triệt tiêu từ trường của nguồn nhiễu.

- Để giảm sự phát xạ từ trường từ tín hiệu trong cáp, tín hiệu phải được che chắn và vỏ cable (cable shield) phải được đặt trên ground plane ở cả hai đầu.

Gợi ý # 7: Đây là độ sâu của da – skin depth được tính cho đồng theo công thức:

trong đó f = tần số [Hz], hằng số từ thẩm μ 0 = 4πE-7 [H/m], σ = độ dẫn điện của đồng 5,96E7 [S/m].

Hướng dẫn EMC # 15 – Giảm thiểu diện tích vòng lặp của tín hiệu trong cáp.

Tăng khả năng miễn nhiễm từ trường, giảm phát xạ trường từ tính

Cách tốt nhất để bảo vệ tín hiệu trong cáp khỏi từ trường là giảm diện tích vòng lặp: Bảo vệ chống lại từ trường H: giảm thiểu diện tích vòng lặp giữa tín hiệu và đường trở lại của nó (ví dụ: sử dụng cặp xoắn hoặc sử dụng dây dẫn liền kề trong cáp dẹt).

Gợi ý # 8: Bản chất của vỏ cable (cable shield) cáp làm bằng đồng hoặc nhôm KHÔNG bảo vệ các tín hiệu trong cáp được che chắn khỏi từ trường. Một vỏ cable (cable shield) cáp bảo vệ khỏi điện trường.

Tham khảo: https://www.academyofemc.com/