Nhiễu điện từ (EMI) gắn liền với mọi thiết bị điện tử mà chúng ta sử dụng ngày nay. Nếu bạn bật bộ radio và TV đồng thời, bạn sẽ gặp phải nhiễu do TV làm nhiễu tín hiệu radio và ngược lại. Chúng ta cũng có thể trải nghiệm điều này khi lên máy bay và được phi hành đoàn yêu cầu tắt các thiết bị điện tử. Điều này nhằm tránh nhiễu tín hiệu thiết bị di động và điện tử với tín hiệu điều hướng của máy bay. Vì nhu cầu điện tử tiêu dùng cao, các tác động của EMI phải được xem xét. Sẽ rất khó chịu nếu một người đi bộ xuống vỉa hè nói chuyện trên điện thoại di động của họ gây nhiễu cho thiết bị âm thanh của người khác. Không thể loại bỏ hoàn toàn EMI / EMC, nhưng chúng ta có thể hạn chế ảnh hưởng bởi các hiệu ứng EMI / EMC.

Một hệ thống điện tử bao gồm bảng mạch in (PCB), chip tích hợp, kết nối và cáp I/O. Ở tần số cao tùy thuộc vào độ dài của các kết nối và dòng điện được mang bởi các dây dẫn, các kết nối có xu hướng hoạt động như ăng-ten, dẫn đến EMI. Các bức xạ EMI này gây nhiễu cho các thiết bị khác có mặt ở khu vực lân cận. Có các tiêu chuẩn quốc tế hạn chế mức độ phát xạ. Do đó, việc đo bức xạ điện từ và kiểm soát các bức xạ này là rất quan trọng.

Vì vậy, bất kỳ sản phẩm nào có dây dẫn / trace và hoạt động ở tần số cao đều có xu hướng bức xạ sóng vô tuyến. Đây là lý do tại sao nghiên cứu và phân tích EMI / EMC là quan trọng. Bức xạ của sản phẩm của bạn có ảnh hưởng các thiết bị khác có mặt gần đó không? Liệu nó có nằm trong các tiêu chuẩn đã đặt ra hay không? Các tiêu chuẩn EMI liên quan như tiêu chuẩn IPC CISPR có đạt được không?

Trong bài viết này, chúng tôi sẽ đề cập đến các hướng dẫn thiết kế PCB bằng cách sử dụng EMI và EMC có thể được kiểm soát / tránh.

- EMI và EMC trong PCB là gì?

- Thiết kế PCB tuân thủ EMC

- Nguồn gây ra EMI là gì?

- Hướng dẫn thiết kế để giảm EMI và EMC trong PCB

- Kiểm tra EMI / EMC trong thiết kế PCB

- Tiêu chuẩn EMI / EMC là gì? (CISPR)

- Phần kết luận

EMI và EMC trong PCB là gì?

Khả năng tương thích điện từ (EMC) là khả năng của một hệ thống điện tử hoạt động trong môi trường điện từ mà không tạo ra EMI (nhiễu điện từ) trong các thiết bị / hệ thống gần đó. EMC đảm bảo rằng hệ thống phải hoạt động như mong muốn theo các biện pháp an toàn đã xác định.

EMI là một nhiễu điện từ, trong đó năng lượng được truyền qua bức xạ / dẫn truyền từ thiết bị điện tử này sang thiết bị điện tử khác và làm thay đổi chất lượng tín hiệu gây ra sự cố. EMI tập trung vào các yêu cầu kiểm tra và giao thoa giữa các thiết bị lân cận. Nó có thể xảy ra trong bất kỳ dải tần số nào, có thể xảy ra với cả với tín hiệu DC. Thông thường, nó xảy ra trên 50MHz.

Bất cứ khi nào một thiết bị khác với các tiêu chuẩn đã xác định, EMC / EMI sẽ thống trị hiệu suất của hệ thống. Vì vậy, điều quan trọng là phải kiểm soát EMI trong giai đoạn đầu của thiết kế PCB. Kiểm soát EMI trong các giai đoạn sản xuất sau này có thể rủi ro về mặt chi phí. Để thiết kế bo mạch thân thiện với EMC, mối quan tâm chính của bạn nên là lựa chọn linh kiện, thiết kế mạch và thiết kế bố trí PCB. Để sẵn sàng đưa ra thị trường, sản phẩm của bạn phải đạt được các tiêu chuẩn EMI / EMC theo quy định.

Thiết kế PCB tuân thủ EMC

Việc áp dụng các thông lệ EMC tốt nhất vào thiết kế PCB giúp đạt được sự tuân thủ các tiêu chuẩn EMC với tỷ lệ thấp hơn nhiều so với các biện pháp EMC thay thế ở mức độ tích hợp cao hơn. Khi nào bạn có thể gọi một thiết kế PCB tuân thủ EMC? Khả năng tương thích của EMC phụ thuộc vào ba quan điểm:

- Nó không được gây ảnh hưởng lên các hệ thống khác.

- Nó không được thể hiện sự nhạy cảm với phát xạ từ các hệ thống khác.

- Và quan trọng nhất, nó không được gây nhiễu cho chính nó.

Các nguồn gây ra EMI là gì?

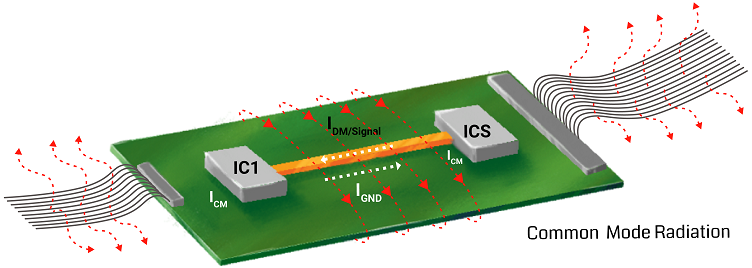

EMI cấu thành cả bức xạ chế độ common và bức xạ chế độ differential.

Có hai loại phát xạ điện từ; dẫn và bức xạ phát xạ. Phát xạ dẫn vào hệ thống thông qua các đường dây và cáp điện đầu vào. Trong khi đó, phát xạ bức xạ xảy ra do sóng điện từ nguồn điện và đường dây thông tin liên lạc, thiết bị đóng cắt và phóng điện tĩnh điện. Nó lan truyền trong không khí từ các thiết bị điện tử và trace, để can thiệp vào các hệ thống điện tử khác. Ví dụ như điện thoại di động và máy tính xách tay can thiệp vào thiết bị điện tử máy bay. Có thể giảm thiểu nhiễu dẫn truyền bằng cách đưa các bộ lọc đường dây được kết nối gần với nguồn điện đầu vào hoặc gần các đầu nối. Một phương pháp hiệu quả khác để giảm nhiễu dẫn là sử dụng lõi ferit / vòng ferit. Lõi Ferrite sử dụng khả năng tiêu tán dòng điện tần số cao trong một loại gốm ferit để chế tạo các thiết bị triệt tiêu nhiễu tần số cao.

Có thể giảm nhiễu dẫn bằng cách sử dụng lõi ferrite / vòng ferrite.

Sự phát xạ điện từ cũng có thể xuất hiện từ các trace tần số cao. Tương tự, chúng có thể tạo ra từ các plane nguồn và đất, do thực hiện decoupling không tốt. Điều này cũng dẫn đến các dòng điện không chủ ý, chẳng hạn như dòng điện ở chế độ common (CM) và chế độ differential (DM).

Các phương pháp decoupling không tốt dẫn đến dòng điện chế độ common (CM) và chế độ differential (DM) không chủ ý.

Bạn có thể nhớ lại định luật Faraday từ các lớp trước của bạn không? Định luật Faraday phát biểu rằng từ trường do cuộn dây tạo ra tỷ lệ thuận với diện tích của cuộn dây và cường độ dòng điện.

E = di / dt ∝ Diện tích cuộn dây ∝ Dòng điện chạy qua cuộn dây

Bây giờ, điều đầu tiên trở nên quan trọng là giảm diện tích cuộn dây/vòng lặp loop. Khi diện tích vòng lặp này giảm, từ thông cũng sẽ giảm. Bây giờ, câu hỏi là, làm thế nào chúng ta có thể làm điều đó? Giả sử, chúng ta có một trace trên lớp PCB trên cùng, chúng ta có thể giảm vòng lặp bằng cách đặt một plane đất trực tiếp dưới trace / tín hiệu. Vì vậy, khi chúng ta làm điều này, dòng điện đi qua trace theo thiết bị và trở về (return path) qua plane đất. Độ dày của PCB là khoảng 3 mils (1 phần 3000 của inch), và do đó diện tích trở nên rất nhỏ. Đây là cách đặt plane GND chính xác bên dưới trace làm giảm EMI vì nó làm giảm diện tích tổng thể được truyền qua.

Điều thứ hai là giảm thiểu tốc độ thay đổi của dòng điện vì dòng điện cao hơn gây ra nhiều phát xạ hơn. Vì vậy, nếu bạn giảm dòng điện, EMI cũng có thể được giảm. Duy trì thời gian tăng (rise time) thấp, ngay cả khi PCB của bạn đang hoạt động ở tần số cao, cũng có thể hữu ích cho việc giảm EMI.

Tránh sai lệch trở kháng: Một hệ thống được thiết kế phù hợp luôn đi kèm với trở kháng phù hợp từ nguồn, đến đường truyền và tải. Nó cung cấp khả năng truyền tải điện năng tối đa và giảm thiểu phản xạ. Phản xạ trên đường truyền làm tăng sóng hài, làm tăng phát xạ bức xạ. Trở kháng không đối sánh gây ra hiện tượng ringing và overshoot trong tín hiệu kỹ thuật số, dẫn đến phát xạ nhiều hơn. Cần có trở kháng phù hợp vì chúng làm giảm phát xạ bức xạ từ thiết bị.

Hướng dẫn thiết kế để giảm EMI và EMC trong PCB

Làm thế nào để thiết kế một bảng mạch có nhiễu điện từ thấp hoặc tuyệt đối không? Chà, không phải là không thể. Các phương pháp thiết kế dưới đây sẽ đảm bảo bạn không tạo ra ăng-ten, thứ sẽ phát ra năng lượng điện từ. Các phương pháp thiết kế tốt nhất này sẽ làm giảm chiều dài và diện tích của các đường trở về (return path) tiềm ẩn có thể làm tăng lượng phát xạ EM không mong muốn. Stack-up nhiều lớp sẽ đóng một vai trò quan trọng, đặc biệt là trong các ứng dụng kỹ thuật số và công suất cao. Các trace tín hiệu từ các linh kiện đến bộ xử lý phải được định tuyến đúng cách để tránh bất kỳ đường trở về nào, cái mà có thể dẫn đến việc tạo ra tín hiệu ở chế độ chung.

Việc sử dụng các linh kiện dán (SMD) thay vì các thiết bị có dây dẫn (linh kiện cắm…) sẽ giảm hơn nữa các vấn đề về EMI / EMC. Linh kiện dán (SMD) cung cấp điện cảm thấp hơn khi so sánh về năng lượng RF. Ngoài ra, linh kiện SMD cung cấp mật độ cao hơn do các vị trí linh kiện được đặt gần nhau hơn. Điều này đặc biệt quan trọng trong bảng mạch hai lớp hoặc bốn lớp. Tuy nhiên, sự phức tạp ngày càng tăng trong thiết kế PCB sẽ tạo ra nhiều vấn đề hơn liên quan đến khoảng cách trace, linh kiện. Kích thước vật lý dày đặc của SMD sẽ giúp kiểm soát nhiễu hiệu quả hơn.

Các linh kiện được dẫn điện có điện cảm cao hơn sẽ tạo ra tần số cộng hưởng hơn 100MHz. Do đó, việc sử dụng một số lượng lớn các linh kiện chân xuyên lỗ không được khuyến khích vì chúng tạo ra nhiễu nhiều hơn linh kiện chân SMD.

1. Khoảng cách trace và bố trí layout

Trace là các đường dẫn điện mang dòng điện từ bên phát/bên nguồn đến thiết bị thu trên PCB. Khi những trace này đi qua bất kỳ khúc cua hoặc đường chéo nào, chúng sẽ tạo thành một ăng-ten bức xạ. Một số quy tắc thiết kế trace phổ biến là:

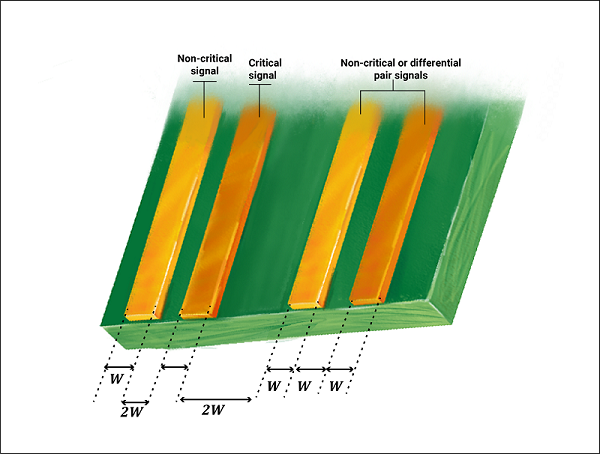

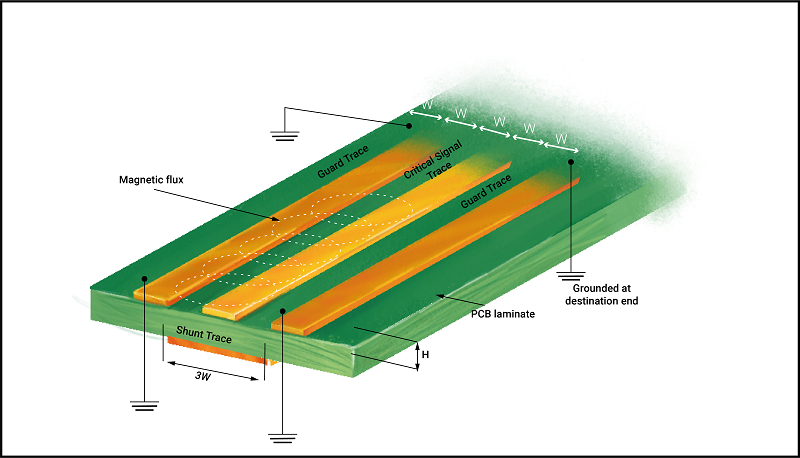

1.1 Phân loại trace: Tất cả các tín hiệu (clock, video, âm thanh, thiết lập lại, v.v.) phải được tách khỏi các trace khác. Quy tắc chung nói rằng khoảng cách giữa các trace nên là 3W, trong đó ‘W’ là chiều rộng của trace. Thực hành này giúp giảm nhiễu xuyên âm và ghép nối giữa các trace liền kề trên cùng một lớp PCB. Vẫn có ngoại lệ đối với quy tắc này.

Các trace liền kề trên cùng một lớp PCB nên cách nhau 3W.

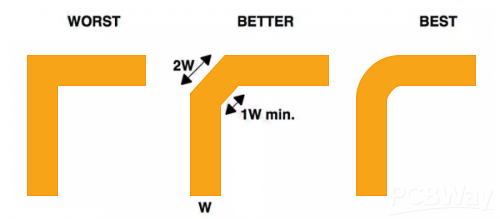

1.2 Tránh góc 90 và xoay 45 °: Khi một trace gặp phải một khúc uốn 90 °, điện dung sẽ tăng lên, dẫn đến sự thay đổi giá trị trở kháng đặc tính, dẫn đến phản xạ. Có thể tránh được bằng cách thay thế những khúc cua gấp bằng những khúc cua 45 °.

Có thể tránh phản xạ bằng cách thay thế những khúc cua gấp bằng những khúc uốn 45 °.

1.3 Định tuyến các trace differential một cách chặt chẽ: Nó làm tăng hệ số ghép nối và giữ cho nhiễu ở chế độ chung common. Ví dụ, chúng ta hãy giả sử hai dây, được đặt gần nhau. Bất kỳ nhiễu bên ngoài nào can thiệp vào hai trace này sẽ thêm cùng một lượng nhiễu trong cả hai trace. Nếu trace 1 có 1 V và trace2 có 1,5 V thì sự khác biệt sẽ là 0,5 V. Vì, nhiễu bên ngoài giống nhau trên cả hai trace, chẳng hạn 0,1 V. Vì vậy, trace 1 sẽ trở thành 1,1 V và trace 2 sẽ trở thành 1,6 V. Và khi bạn tính toán sự khác biệt, nó vẫn giống nhau là 0,5 V. Vì vậy, nhiễu thực sự sẽ bị triệt tiêu. Đó là lý do tại sao các tín hiệu tốc độ cao được ưu tiên định tuyến dưới dạng các cặp vi sai differential.

1.4 Sử dụng vias một cách thuần thục: Vias được sử dụng trong PCB nhiều lớp cho mục đích định tuyến tín hiệu. Một nhà thiết kế giỏi phải biết rằng mỗi via đi kèm với hiệu ứng điện dung và điện cảm của nó. Vì vậy, vias nên được hạn chế càng ít càng tốt và các trace quan trọng nên được định tuyến trên cùng một lớp. Do điện dung và độ tự cảm ký sinh trong vias, có sự không phù hợp trở kháng giữa qua và trace, tạo ra phản xạ. Khi không thể hạn chế được vias, cần đảm bảo rằng vias plane đất phải được đặt gần với vias tín hiệu. Điều này sẽ đảm bảo rằng các tín hiệu được tham chiếu đến GND và điều này làm giảm sự thay đổi trong giá trị trở kháng (cái mà gây ra phản xạ). Trong các cặp vi sai, khi không thể hạn chế được vias, thì nên đặt cùng một số lượng vias cho cả hai trace.

Mẹo: Tránh vias trong các trace differential. Nếu bạn phải sử dụng via thì anti-pad được chia sẻ bởi hai vias để giảm thiểu điện dung ký sinh.

1.5 Tránh hiện tượng stub ở các trace nhạy cảm và tần số cao: Các trace stub tạo ra phản xạ cũng như tiềm năng thêm ăng ten bước sóng phân đoạn vào mạch.

1.6 Sử dụng các trace bảo vệ và shunt cho các đường dây clock: Trong các mạch clock, các tụ điện decoupling rất quan trọng để khử nhiễu lan truyền dọc theo đường cung cấp. Các trace bảo vệ và shunt được sử dụng để bảo vệ các đường clock khỏi các nguồn EMI, nếu không, các tín hiệu clock như vậy sẽ tạo ra các vấn đề ở những nơi khác trong mạch.

Các trace bảo vệ và shunt được sử dụng để bảo vệ các đường clock khỏi các nguồn EMI.

2. Plane đất

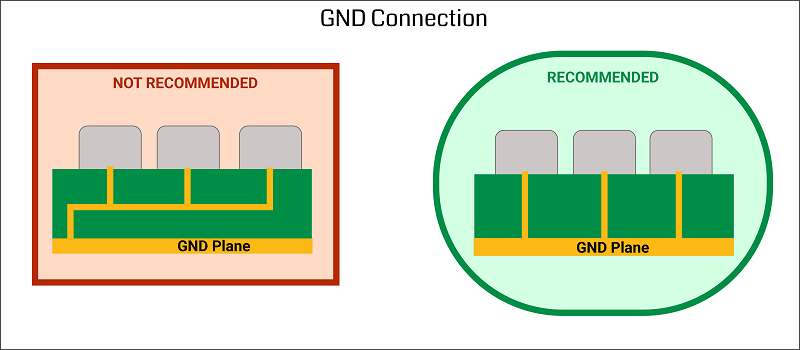

Đất GND có giá trị điện cảm thấp là một yếu tố quan trọng trong quá trình thiết kế PCB để giảm thiểu các vấn đề về EMC. Tăng diện tích plane đất trên PCB làm giảm điện cảm đất trong hệ thống, giảm phát xạ EM và nhiễu xuyên âm. Một số cách tiếp cận có sẵn khi chúng ta cần kết nối các tín hiệu với plane đất, nhưng cách nào là tốt nhất? Trước khi chuyển sang cách tiếp cận thiết kế PCB tốt nhất, chúng ta hãy thảo luận về điều gì là không thể chấp nhận được? Không bao giờ kết nối ngẫu nhiên các thành phần PCB với các điểm nối đất. Vì vậy, cách tiếp cận thiết kế được đề xuất là gì?

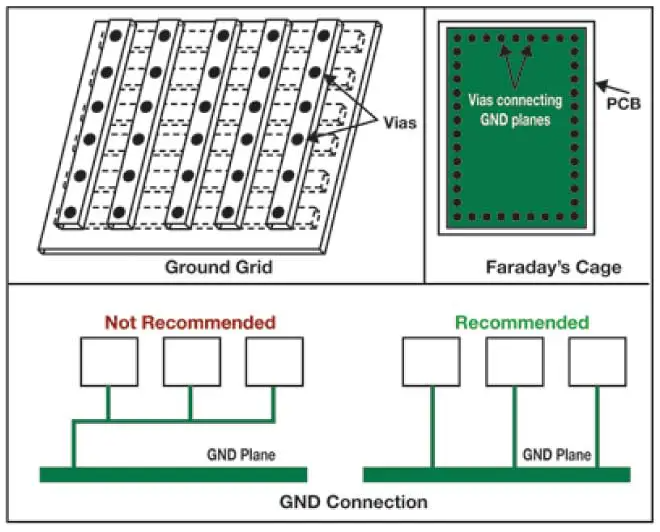

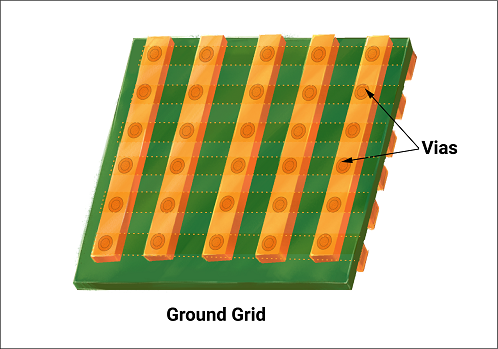

2.1 Sử dụng toàn bộ plane đất và lưới nối đất: Sử dụng toàn bộ plane đất vì nó cung cấp giá trị điện cảm nhỏ nhất khi tín hiệu trở về nguồn từ tải. Mặc dù plane đất yêu cầu một lớp PCB chuyên dụng, nhưng điều này có thể không phải lúc nào cũng khả thi với PCB hai lớp. Trong các tình huống như vậy, các nhà thiết kế sử dụng lưới nối đất, trong đó điện cảm của lưới nối đất phụ thuộc vào khoảng cách giữa các lưới.

Lưới nối đất được sử dụng khi không có lớp PCB chuyên dụng.

2.2 Tránh các đường trở về (return path) dài: Theo định luật Faraday, cách một tín hiệu trở về (return path) qua plane đất của hệ thống sẽ tạo nên sự khác biệt. Khi một tín hiệu đi một đường dài hơn, nó sẽ tạo ra một vòng lặp plane đất tạo thành một ăng-ten bức xạ. Một đường trở lại ngắn có trở kháng thấp hơn, mang lại hiệu suất EMC tốt hơn. Các đường trở lại dài tạo ra sự ghép nối (coupling) lẫn nhau lớn hơn dẫn đến nhiễu xuyên âm. Do đó, hãy giữ cho các đường trở lại càng ngắn càng tốt và diện tích vòng lặp càng nhỏ càng tốt. Đường trở về dòng điện phải được xử lý chính xác.

Một đường trở lại ngắn có trở kháng thấp hơn, mang lại hiệu suất EMC tốt hơn.

Nên kết nối plane đất của thiết bị trực tiếp với plane đất. Điều này sẽ làm giảm các vòng lặp đất.

Luôn kết nối plane đất của thiết bị trực tiếp với plane đất.

2.3 Sử dụng lồng / vòng bảo vệ của Faraday để cách ly môi trường nhiễu: Một lồng Faraday được tạo ra bằng cách thêm đất trên cạnh của PCB. Mục đích là không định tuyến bất kỳ tín hiệu nào bên ngoài ranh giới này. Kỹ thuật này hạn chế phát xạ / nhiễu trong giới hạn xác định.

Lồng của Faraday hạn chế phát xạ / nhiễu trong khu vực xác định.

2.4 Đặt mạch tốc độ cao gần plane đất hơn và mạch tốc độ thấp gần plane nguồn hơn.

2.5 Luôn nối đất các khu vực lấp đầy đồng: Các khu vực đồng floating (không nối đi đâu) phải luôn được nối đất. Nếu không, nó có thể hoạt động như một ăng-ten, gây ra các vấn đề về EMC.

2.6 Kiểm tra các yêu cầu đa nguồn (multi-power): Khi một mạch yêu cầu nhiều hơn một nguồn điện, thì cách tốt nhất là giữ chúng cách nhau bằng một plane nối đất. Nhưng các plane đa plane đất không thể được thực hiện trong PCB một lớp. Vấn đề này có thể được giải quyết bằng cách chạy đường dây điện và đường nối đất cho một nguồn cung cấp tách biệt với các nguồn khác. Nó cũng sẽ tránh việc ghép nhiễu (noise coupling) từ nguồn điện này sang nguồn điện kia.

2.7 Cẩn thận với các Split apertures: Các Split apertures là các lỗ dài và via rộng trong nguồn điện và các plane tạo ra một khu vực không đồng nhất. Sự không đồng nhất này làm tăng trở kháng trong plane nguồn và plane đất.

3. Che chắn (Shielding)

Che chắn là một kỹ thuật cơ khí sử dụng vật liệu dẫn điện / từ tính (hoặc cả hai) để ngăn chặn EMI trong hệ thống. Tấm chắn cơ học là một vật chứa dẫn điện kín được kết nối với plane đất, có tác dụng làm giảm kích thước của anten vòng bằng cách hấp thụ và phản xạ một phần bức xạ của chúng. Nó có thể được sử dụng để bao phủ toàn bộ hệ thống hoặc một phần của nó, tùy theo yêu cầu. Che chắn EMI / EMC bảo vệ việc truyền tín hiệu khỏi nhiễu bên ngoài và ngăn ngừa mất thông tin.

EMI / EMC che chắn bảo vệ tín hiệu khỏi nhiễu bên ngoài.

3.1 Che chắn cáp (Cable shielding): Cáp mang tín hiệu tương tự và kỹ thuật số tạo ra các vấn đề nghiêm trọng về EMI. Các yếu tố điện dung và điện cảm ký sinh của chúng là nguyên nhân gây ra điều này. EMI có thể được ngăn chặn bằng cách che chắn các cáp này và kết nối chúng với plane đất ở phía trước và phía sau.

4. Sắp xếp các lớp PCB (stack-up):

Hiệu suất EMC của PCB cũng phụ thuộc vào sự sắp xếp các lớp của nó. Trong trường hợp có hai hoặc nhiều hơn hai lớp, nên sử dụng toàn bộ một lớp làm plane GND. Đối với bảng bốn lớp, lớp bên dưới lớp plane đất nên được sử dụng làm plane nguồn. Stack ưu tiên cho bảng bốn lớp là signal1, đất, nguồn và signal 2. Các trace trở kháng phải nằm trên signal1 càng xa càng tốt.

4.1 Nếu sử dụng mạch hai lớp và không thể sử dụng toàn bộ một lớp làm plane GND thì nên sử dụng lưới tiếp đất.

4.2 Nếu không sử dụng plane nguồn riêng, thì các đường nối đất phải chạy song song với các đường nguồn để giữ cho nguồn cung cấp “sạch” nhiễu.

4.3 Khi có nhiều hơn bốn lớp, nên sử dụng cách sắp xếp các lớp PCB như lớp tín hiệu → lớp đất / nguồn → lớp tín hiệu → lớp đất / nguồn → lớp tín hiệu → lớp đất / nguồn → lớp tín hiệu. Đó là sử dụng các lớp tín hiệu và plane đất xen kẽ. Và số lượng các lớp phải là số chẵn.

Hiệu suất EMC của PCB cũng phụ thuộc vào sự sắp xếp các lớp của nó.

5. Tách biệt các linh kiện nhạy cảm

Để có thiết kế thân thiện với EMC, các thành phần PCB cần được nhóm lại theo các tín hiệu mà chúng đang hoạt động, chẳng hạn như tín hiệu tương tự, kỹ thuật số, nguồn cung cấp, tín hiệu tốc độ thấp, tốc độ cao , v.v. Các đường dẫn tín hiệu cho từng nhóm thành phần nên ở trong khu vực xác định của chúng. Tốt nhất là sử dụng bộ lọc (filter), bất cứ khi nào tín hiệu phải truyền từ hệ thống con này sang hệ thống con khác.

Các thành phần PCB cần được nhóm lại theo loại tín hiệu mà chúng đang hoạt động.

6. Tụ điện Decoupling

Khi IC hoạt động, chúng chuyển đổi dòng điện ở tần số cao, dẫn đến nhiễu chuyển mạch trong các trace/nhánh nguồn kết nối với IC. Nhiễu này nếu không được kiểm soát, sẽ dẫn đến phát xạ bức xạ và do đó là EMI. Các phương pháp để giảm nhiễu của đường nguồn là đặt các tụ điện decoupling gần các chân nguồn của IC. Và nối đất trực tiếp các tụ điện với plane đất. Việc sử dụng plane nguồn thay vì trace nguồn cũng sẽ làm giảm nhiễu cho nguồn.

Nhiễu của đường nguồn được giảm bớt bằng cách đặt các tụ điện decoupling gần các chân nguồn của IC.

7. Kiểm soát trở kháng cho thiết kế đường truyền dẫn transmission line

Khi một mạch hoạt động ở tốc độ cao, sự hòa hợp trở kháng giữa bên phát và bên nhận/thu trở nên quan trọng. Nếu trở kháng không được hòa hợp và điều khiển thích hợp thì nó sẽ gây ra hiện tượng phản xạ tín hiệu và ringing tần số cao. Năng lượng RF dư thừa được tạo ra do ringing và phản xạ, sẽ bức xạ / ghép nối coupling đến các phần khác của mạch, tạo ra các vấn đề về EMI. Các chiến lược termination tín hiệu giúp giảm thiểu những tác dụng không mong muốn này. Termination không chỉ giảm thiểu phản xạ tín hiệu và ringing bằng các biện pháp trở kháng có kiểm soát mà còn có thể làm chậm lại các sườn lên và sườn xuống của tín hiệu. Trở kháng của các trace cũng phụ thuộc vào vật liệu PCB được sử dụng trên bo mạch.

Chiến lược Termination thích hợp giúp giảm ringing.

Kiểm tra EMI / EMC trong thiết kế PCB

Sự phát xạ điện từ trong một hệ thống điện tử được đo bằng cách thực hiện các kỹ thuật mô hình hóa khác nhau. Mô phỏng máy tính thường được coi là cách tiếp cận cơ bản trong phân tích EMC. Mô phỏng máy tính được thực hiện thông qua một kỹ thuật tích hợp để có được một phép đo chính xác các thông số thiết yếu. Sau đây là một số bước để kiểm tra sự phát xạ điện từ trong một hệ thống điện tử:

- Mô hình miền thời gian chênh lệch hữu hạn được thực hiện để đo đáp ứng tần số của dòng điện chế độ chung common mode trong các ứng dụng điện áp cao.

- Dòng điện ở chế độ chung common mode được đánh giá bằng cách xem xét các yếu tố như trở kháng của ăng ten current-mode và hằng số mạch phân tán.

- Sự kết hợp coupling điện giữa plane nguồn và plane đất cũng sẽ tác động đến dòng điện ở chế độ chung common mode.

Sierra Circuits đo phản ứng tần số của phát xạ điện từ từ cấu trúc stripline với sự trợ giúp của một công cụ cao cấp và mô hình đề xuất của riêng chúng tôi. Chúng tôi hiểu tầm quan trọng của việc ngăn chặn EMI, do đó chúng tôi cung cấp những hiểu biết vật lý và hướng dẫn thiết kế để giữ cho mạch của bạn an toàn và hoạt động tốt.

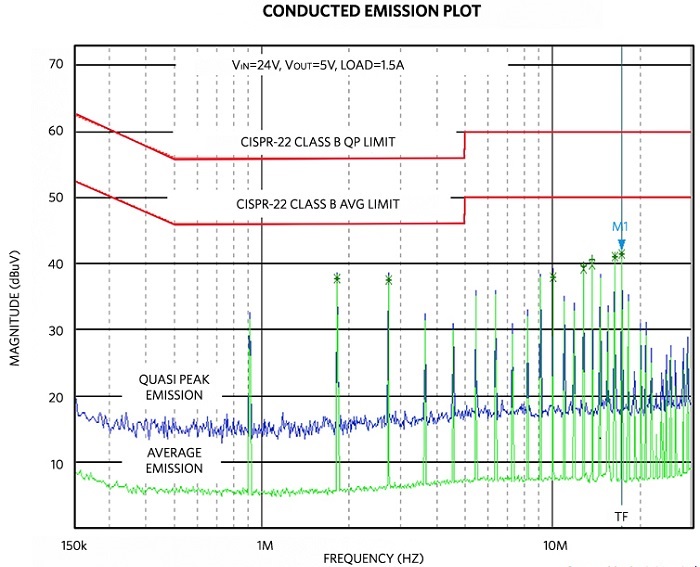

Đáp ứng các tiêu chuẩn EMI / EMC (CISPR, FCC phần 15)

Mục tiêu của các tiêu chuẩn EMC / EMI là duy trì khả năng tương thích giữa hệ thống điện và điện tử đặt chung để vận hành không gặp sự cố. Tiêu chuẩn CISPR có thể áp dụng cho tất cả các sản phẩm, hệ thống và cách lắp đặt. Chúng được giới thiệu theo Phần 15 của Ủy ban Truyền thông Liên bang (FCC) và các quy định của Ủy ban Đặc biệt Quốc tế Châu Âu về Nhiễu vô tuyến (CISPR).

Các tiêu chuẩn xác định các giới hạn cho phép đối với cả phát xạ dẫn và phát xạ và phân loại chúng vào các môi trường dân cư, thương mại, công nghiệp... Để đáp ứng các yêu cầu của EMC, thiết bị phải được kiểm tra phát xạ dẫn và bức xạ cùng với tính nhạy cảm dẫn và bức xạ. Ví dụ về một trong các bài kiểm tra được hiển thị bằng biểu đồ dưới đây. Có các giới hạn trên đồ thị này và các mức phát xạ phải nằm trong các giá trị được đề cập trong đồ thị.

Phát xạ EMI / EMC phải theo tiêu chuẩn FCC CISPR. Hình ảnh: Maxim Integrated

Phần kết luận

Một mạch điện tử được tạo thành từ một số linh kiện điện tử được sắp xếp theo một cách thức xác định trước. Nếu sự sắp xếp không phù hợp, nó có thể gây ra nhiều vấn đề về EMI / EMC. Việc thiết kế một PCB cho bất kỳ thành phần nào có ảnh hưởng lớn đến hiệu suất EMC của nó và lượng EMI được tạo ra. Trong khi thiết kế PCB, bạn cần lưu ý đến hiệu ứng EMI / EMC của từng thành phần. Hiệu suất EMC tốt chỉ có thể đạt được khi thực hành thiết kế PCB tốt, trong đó nhà thiết kế phải loại bỏ nguồn nhiễu hoặc bảo vệ mạch khỏi các tác động bất lợi của nó. Cuối cùng, mục tiêu là duy trì chức năng mong muốn của bảng mạch để có EMC tốt hơn.

Dịch từ bài: https://www.protoexpress.com/blog/7-pcb-design-tips-solve-emi-emc-issues/