PCB 2 lớp là người bạn tốt nhất của người có sở thích. Chúng rất dễ xác định trong phần mềm thiết kế của bạn và việc định tuyến rất đơn giản nếu số lượng dây đủ thấp. Mặc dù tôi thường không làm việc với những thứ chỉ có thể thực hiện trên 2 lớp, nhưng điều quan trọng là phải biết cách sử dụng những bảng này đúng cách. Nếu khéo léo, bạn thậm chí có thể sử dụng những bảng này để định tuyến một số giao tiếp tốc độ cao.

Trong bài viết này, tôi muốn xem xét một số quy tắc quan trọng để thiết kế PCB 2 lớp sẽ sử dụng giao tiếp nối tiếp tốc độ cao. Những thứ như USB hoặc SPI có thể được thực hiện dễ dàng trên bảng mạch 2 lớp miễn là tuân theo một số quy tắc định tuyến cơ bản. Những gì tôi sẽ trình bày dưới đây sẽ là điểm khởi đầu để định tuyến tín hiệu số trong bố cục PCB 2 lớp.

Một điểm cần lưu ý: bạn không nên vào dự án 2 lớp như thế này với mong muốn bo mạch này sẽ vượt qua bài kiểm tra EMC. Việc đảm bảo EMC sẽ phụ thuộc vào nhiều yếu tố liên quan đến nguồn điện, nối đất, bọc shield của bạn, các thành phần và mạch điện nào trên bo mạch và nhiều yếu tố khác. Hy vọng rằng điều này sẽ giúp bạn có phần giới thiệu hữu ích về cách bạn có thể hoàn thành phần định tuyến layout của PCB 2 lớp mà không tạo ra các vấn đề về tính toàn vẹn tín hiệu.

Bắt đầu với bảng mạch 2 lớp

Bố cục PCB 2 lớp rất thú vị vì chúng thường là cấp độ đầu vào của hầu hết các nhà thiết kế. Hầu hết các thiết kế liên quan đến MCU tốc độ vừa phải (có thể là thời gian tăng 5-10 ns), một bus nối tiếp thông thường như SPI và các giao tiếp kỹ thuật số tốc độ cao đơn giản hơn có thể hoạt động tốt trên bảng 2 lớp miễn là chúng không quá dày đặc và bạn không vi phạm một số quy tắc định tuyến cơ bản . Tuy nhiên, những thiết kế này thường phá vỡ nhiều quy tắc về tính toàn vẹn của tín hiệu và tạo/nhận EMI quá mức. Kết quả là về mặt kỹ thuật, bo mạch có thể hoạt động như bạn dự định, nhưng nó có thể không bao giờ vượt qua thử nghiệm EMC, vì vậy bạn sẽ không thể bán nó.

Trước tiên, có một số điểm cần lưu ý trong thiết kế bảng 2 lớp sử dụng tín hiệu số:

- Kiểm soát trở kháng: Có bất kỳ giao tiếp nào của bạn yêu cầu kiểm soát trở kháng không? Nếu vậy, chỉ cần nhớ rằng có thể khó đạt được yêu cầu trở kháng trên độ dày PCB tiêu chuẩn đối với tín hiệu single-end.

- Độ dài trace: Bởi vì chúng tôi không thể đạt được các yêu cầu kiểm soát trở kháng trên bảng 2 lớp, nên chúng tôi sẽ phải giữ độ dài trace dưới một số độ dài tới hạn . Một số giao tiếp rất dễ tha thứ với trở kháng và có độ dài tới hạn dài, nhưng bạn sẽ cần tính toán giới hạn độ dài.

- Truy cập vào mặt đất: Để đảm bảo nhiễu xuyên âm thấp và EMI thấp trong định tuyến kỹ thuật số của bạn, bạn sẽ cần cung cấp quyền truy cập vào mặt đất với đường dẫn trở lại rõ ràng .

- Số lượng linh kiện/tín hiệu: Trên bo mạch 2 lớp, bạn có không gian hạn chế để định tuyến, do đó bạn không thể có quá nhiều linh kiện. Ngay khi bạn cố gắng bao gồm quá nhiều linh kiện và có nhiều điểm giao nhau trong định tuyến của mình, bạn sẽ phải chuyển sang bảng 4 lớp, hoặc bạn sẽ phải làm bảng 2 lớp của mình quá lớn.

Tín hiệu số và trở kháng

Khi làm việc với logic kỹ thuật số, đặc biệt là trong bo mạch 2 lớp, điều quan trọng cần lưu ý là không phải tất cả các tín hiệu kỹ thuật số đều có yêu cầu trở kháng. Đôi khi, nếu có, bạn có thể vi phạm và giao tiếp sẽ hoạt động tốt. Điều này rất quan trọng trong bo mạch 2 lớp vì nếu bạn chỉ muốn định tuyến các trace dạng microstrip, thì độ rộng của trace của bạn cần phải có một giá trị cụ thể để đạt được mục tiêu trở kháng.

Thông thường, mục tiêu trở kháng bạn nhìn thấy đối với tín hiệu số sẽ như sau:

- Một số yêu cầu trở kháng single-end, trong đó tín hiệu đơn, riêng biệt

- Một số yêu cầu trở kháng vi sai đối với các cặp vi sai, trong đó các tín hiệu phải được định tuyến cùng nhau

Ví dụ, hãy xem xét một bảng mạch 2 lớp có lõi tiêu chuẩn dày 62 mil (Dk = 4,8). Nếu chúng ta muốn đạt được mục tiêu trở kháng tiêu chuẩn 50 Ohms thì chúng ta cần phải có chiều rộng trace gần 110 mils! Đây là một độ rộng trace rất lớn và lớn hơn nhiều so với kích thước pad của bất kỳ linh kiện kỹ thuật số nào bạn sẽ đặt trên một bảng mạch. Để xác định điều này, tôi đã sử dụng công cụ tính trở kháng microstrip trực tuyến dựa trên công thức của IPC 2141.

Kết quả tính toán trở kháng cho bo mạch 2 lớp đơn giản có mặt phẳng tham chiếu.

Máy tính trực tuyến không đưa ra kết quả chính xác nhất, nhưng kết quả trên minh họa một điểm quan trọng: bạn không thể thực hiện kiểm soát trở kháng cho các trace single-end bị cô lập trên PCB 2 lớp và mong muốn phù hợp với mọi thứ trong bố cục. Rõ ràng, điều này sẽ loại bỏ việc sử dụng DDR cho bộ nhớ , bao gồm các trace single-end với tín hiệu tốc độ cao và độ dài điện rất nhỏ.

Đây là nơi chúng tôi cần đặt giới hạn độ dài cho trace của bạn nếu chúng tôi đang sử dụng giao tiếp có kiểm soát trở kháng. Khi khoảng cách mà tín hiệu truyền đi trong thời gian tăng của nó dài hơn nhiều so với chiều dài của đường, thì trở kháng của đường không thành vấn đề. Trong trường hợp này, tín hiệu chỉ nhìn thấy trở kháng của tải trong quá trình truyền. Giới hạn độ dài chính xác phụ thuộc vào nhiều yếu tố, nhưng có một quy tắc rất thận trọng là đặt giới hạn độ dài trace là 1/10 khoảng cách mà tín hiệu truyền đi.

Chỉ là một ví dụ, hãy sử dụng độ trễ lan truyền trong hình ảnh trên với tín hiệu thời gian tăng 5 ns. Trong trường hợp trên, tốc độ lan truyền là khoảng 6,8 inch/ns. Vì vậy, điều này có nghĩa là, nếu chúng ta có tín hiệu thời gian tăng 5 ns thì tín hiệu sẽ truyền đi 34 inch trong thời gian tăng của nó, do đó chiều dài trace tối đa của chúng ta sẽ là 1/10 của tín hiệu này, hoặc 3,4 inch. Trên thực tế, chúng ta có thể ít thận trọng hơn một chút so với giới hạn độ dài 1/10. Nếu chúng ta đặt giới hạn độ dài 1/4, chúng ta sẽ có chiều dài trace tối đa là 8,5 inch trước khi cần bắt đầu lo lắng về trở kháng của trace.

Thời gian tăng chậm so với chiều dài trace được sử dụng để xác minh xem thiết kế có yêu cầu kết hợp trở kháng chặt chẽ trên PCB 2 lớp hay không.

Tùy thuộc vào mức độ vi phạm trở kháng mà bạn có thể chấp nhận ở đầu thu của kênh, bạn chắc chắn sẽ có quyền tự do triển khai bảng 2 lớp với giao thức kỹ thuật số thông thường miễn là độ dài ngắn.

Điều gì về trở kháng vi sai?

Tôi chắc rằng người đọc sẽ biết, hầu hết các giao tiếp tốc độ cao đều quan tâm đến trở kháng vi sai, không chỉ trở kháng single-end. Như chúng ta đã thấy ở trên, trace single-end sẽ cần phải lớn đến mức không thể chấp nhận được để đạt giá trị trở kháng 50 Ohm mà bạn sẽ thấy trong hầu hết các thông số kỹ thuật. Làm thế nào chúng ta có thể đạt được giá trị trở kháng vi sai trên bảng 2 lớp khi yêu cầu về độ rộng trace trở kháng đặc tính quá lớn?

Một số giao tiếp thực sự có thể được định tuyến dưới dạng trace single-end có độ dài phù hợp hoặc dưới dạng cặp vi sai được liên kết chặt chẽ! USB là một ví dụ hoàn hảo: thành phần đầu cuối Termination xử lý từng đầu của cặp riêng lẻ như một trace single-end, vì vậy chúng ta vẫn phải đạt thông số trở kháng single-end. Làm thế nào chúng ta có thể làm được điều này?

Trong trường hợp này, chúng ta cần sử dụng công cụ để tính trở kháng vi sai và sử dụng giá trị độ rộng và khoảng trống trả về đó để đảm bảo chúng ta đạt được thông số kỹ thuật single-end. Trong bảng 2 lớp, chúng ta không thể chỉ lấy chiều rộng mà chúng ta tìm thấy ở trên và đưa nó vào công cụ tính trở kháng vi sai. Nếu làm vậy, chúng ta sẽ thấy rằng khoảng cách trace cần thiết là khoảng 10 inch! Rõ ràng, điều này không thực tế. Trong thực tế, nếu chúng ta tính toán độ rộng trace và khoảng cách mà chúng ta cần cho trở kháng mục tiêu, chúng ta sẽ có chiều rộng gần hơn với chiều rộng 10 mil và khoảng cách 6 mil đối với cách sắp xếp microstrip đồng phẳng. Điều này hợp lý hơn nhiều.

Điều này có nghĩa là gì:

- Độ rộng trace cần thiết trong một cặp vi sai không nhất thiết phải bằng chiều rộng trace cần thiết để đạt trở kháng đặc tính cho một trace. Trong một cặp vi sai, độ rộng trace single-end xác định trở kháng chế độ lẻ, bằng một nửa mục tiêu trở kháng vi sai của bạn. Giá trị trở kháng chế độ lẻ khác với giá trị trở kháng đặc tính.

Đây là single-end hiệu đặc biệt quan trọng. Điều đó có nghĩa là, đối với giao tiếp vi sai, bạn không nên chỉ lấy chiều rộng trace cho trở kháng đặc tính được hiển thị ở trên mà chỉ cần cắm nó vào máy tính trở kháng vi sai để có khoảng cách. Khi các trace trong một cặp vi sai được đưa lại gần nhau, việc ghép giữa chúng sẽ làm giảm trở kháng tín hiệu single-end và khiến chiều rộng trace yêu cầu nhỏ hơn, ngay cả trên PCB 2 lớp. Chúng ta sẽ thảo luận thêm về vấn đề này trong hai bài viết sắp tới về chủ đề này, bao gồm một ví dụ về việc chúng ta xem xét việc sử dụng USB trên bo mạch 2 lớp .

Một số nguyên tắc định tuyến 2 lớp cho tín hiệu số

Mục tiêu của những nguyên tắc cơ bản này là đảm bảo thiết kế kỹ thuật số của bạn có độ nhiễu thấp nhất có thể, điều này khó xảy ra với cấu trúc của bảng 2 lớp.

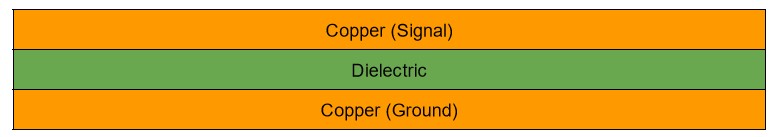

- Đặt mặt phẳng tham chiếu ground ở lớp dưới cùng, sau đó đặt các thành phần kỹ thuật số và định tuyến lên lớp trên cùng. Điều này sẽ không giúp bạn kiểm soát trở kháng trong khi định tuyến, nhưng dù sao bạn cũng nên làm điều này để giúp kiểm soát nhiễu và giúp bạn dễ dàng tiếp cận ground thông qua via.

- Sử dụng chiều rộng trace cố định để định tuyến nguồn và tín hiệu. trace 8-10 mil chỉ phù hợp để định tuyến tín hiệu số và 12-14 mil via phù hợp để chuyển tín hiệu trở lại mặt phẳng mặt đất. Nguồn điện có thể được định tuyến bằng đa giác nếu bạn đang làm việc với dòng điện cao, nhưng trong hầu hết các trường hợp, bạn sẽ ổn với các trace rộng hơn.

- Sử dụng tụ điện decoupling/bypass để đảm bảo nguồn điện ổn định và độ nảy đất thấp. Bo mạch 2 lớp có thể có hiện tượng nảy đất và có thể có một số nhiễu trên đường cấp điện, nhưng các tụ điện decoupling/bypass sẽ làm giảm nhiễu này.

Trong phần tiếp theo của loạt bo mạch 2 lớp của chúng tôi, tôi sẽ trình bày cách triển khai các nguyên tắc thiết kế này cho USB, chắc chắn có thể được coi là giao tiếp kỹ thuật số tốc độ cao. Nếu bạn quen thuộc với USB, bạn sẽ biết rằng đó là giao tiếp nhanh và thường cần định tuyến được kiểm soát bằng trở kháng. Tuy nhiên, với những hướng dẫn được hiển thị ở trên, bạn có thể có được bảng 2 lớp chức năng sử dụng giao tiếp này. Chỉ cần lưu ý rằng bạn có thể không có bo mạch hoàn toàn không có nhiễu, vì vậy đừng mong đợi bố cục này sẽ tự động vượt qua quá trình kiểm tra EMC . Tuy nhiên, nó sẽ hoạt động tốt như một bảng phát triển cho bộ vi điều khiển yêu thích của bạn và bạn có thể gặp may nếu định tuyến tín hiệu của mình một cách chính xác với mặt phẳng tham chiếu liên tục ở lớp ngay bên dưới và bạn hạn chế chuyển lớp thông qua via.