Khi thiết kế PCB cho các ứng dụng tốc độ cao, việc xây dựng stackup (các lớp của PCB) rất quan trọng để đảm bảo hiệu suất điện, độ tin cậy, và khả năng sản xuất. Một stackup tốt giúp tối ưu hóa việc kiểm soát trở kháng, giảm nhiễu xuyên âm (crosstalk), giảm EMI (nhiễu điện từ), và hỗ trợ tín hiệu tốc độ cao. Dưới đây là các bước và nguyên tắc để xây dựng stackup cho PCB tốc độ cao:

1. Xác định số lớp cần thiết

- Tín hiệu và độ phức tạp: Tính toán số lượng tín hiệu và mức độ phức tạp để quyết định số lớp. PCB tốc độ cao thường có từ 4 đến 16 lớp, hoặc nhiều hơn nữa.

- Các lớp nguồn: Xác định số lượng mặt phẳng nguồn (power planes) và mặt phẳng đất (ground planes) cần thiết để hỗ trợ hệ thống.

- Kiểm soát trở kháng: Đối với tín hiệu tốc độ cao, các đường dẫn tín hiệu cần có trở kháng kiểm soát, ví dụ 50Ω (single-ended) hoặc 100Ω (differential pair).

2. Chọn loại vật liệu

- Dielectric constant (Dk): Chọn vật liệu có Dk thấp và ổn định để giảm tổn thất tín hiệu. Ví dụ: FR-4 (thông dụng, chi phí thấp) hoặc vật liệu cao cấp như Rogers.

- Loss tangent (Df): Chọn vật liệu có Df thấp để giảm suy hao tín hiệu.

- Độ dày vật liệu: Đảm bảo độ dày giữa các lớp thích hợp để kiểm soát trở kháng.

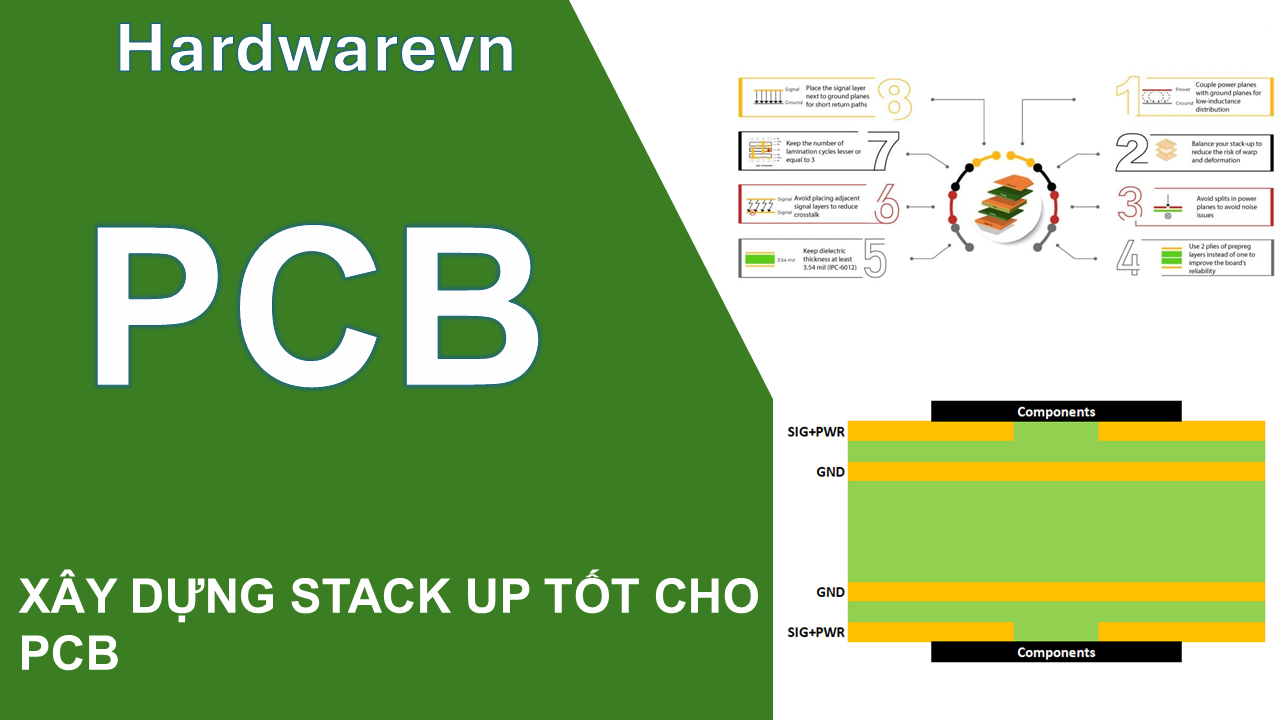

3. Sắp xếp các lớp (Layer stackup)

- Mặt phẳng đồng (Copper planes): Đặt các lớp mặt phẳng đất (GND) và nguồn (Power) sát nhau để tạo hiệu ứng tụ điện và giảm nhiễu.

- Tín hiệu tốc độ cao: Đặt gần mặt phẳng GND để giảm EMI và dễ kiểm soát trở kháng.

Cách sắp xếp tham khảo:

PCB 4 lớp:

- Lớp 1: Tín hiệu (Signal)

- Lớp 2: Ground (GND plane)

- Lớp 3: Nguồn (Power plane)

- Lớp 4: Tín hiệu (Signal)

PCB 6 lớp:

- Lớp 1: Tín hiệu (Signal)

- Lớp 2: Ground (GND plane)

- Lớp 3: Tín hiệu bên trong (Inner signal)

- Lớp 4: Tín hiệu bên trong (Inner signal)

- Lớp 5: Nguồn (Power plane)

- Lớp 6: Tín hiệu (Signal)

4. Kiểm soát trở kháng

Tính toán trở kháng: Sử dụng công cụ như Polar SI9000 hoặc công thức tính trở kháng. Đường truyền tín hiệu:

- Single-ended: 50Ω

- Differential pair: 90-100Ω (tùy giao thức như USB, HDMI).

Khoảng cách lớp: Điều chỉnh khoảng cách giữa các lớp tín hiệu và mặt phẳng để đạt được trở kháng mong muốn.

5. Giảm nhiễu xuyên âm và EMI

- Đặt GND gần tín hiệu: Mỗi lớp tín hiệu nên đặt sát lớp GND để giảm nhiễu.

- Chia power plane: Chia các vùng nguồn khác nhau trên lớp power plane, nhưng giữ cho GND liên tục.

- Đường tín hiệu: Tránh chạy tín hiệu song song quá gần để giảm nhiễu xuyên âm.

6. Cân nhắc về sản xuất

- Độ dày tổng: Xác định độ dày PCB tổng thể (ví dụ: 0.8mm, 1mm, 1.6mm hoặc 2mm).

- Chi phí: PCB nhiều lớp và vật liệu cao cấp sẽ tăng chi phí.

- Dung sai: Cân nhắc dung sai sản xuất khi tính khoảng cách lớp và bề rộng đường tín hiệu.

7. Simulate và kiểm tra

- Công cụ EDA: Sử dụng phần mềm như Altium Designer, Cadence Allegro, hoặc Siemens Xpedition để mô phỏng tín hiệu.

- Kiểm tra EMI/EMC: Kiểm tra tín hiệu và mức độ nhiễu điện từ trước khi sản xuất.

Kết luận

Một stackup tốt cần cân bằng giữa yêu cầu tín hiệu, độ phức tạp thiết kế, và chi phí sản xuất. Luôn kiểm tra và tối ưu qua mô phỏng trước khi sản xuất.