Tôi thỉnh thoảng thấy các câu hỏi trên các diễn đàn, một số bài đăng trên blog và thậm chí cả các ghi chú ứng dụng tiếp tục khuyến nghị sử dụng định tuyến trực giao, thường là trong bảng 2-6 lớp. Khi xem các ghi chú ứng dụng, tôi có xu hướng mặc định lời khuyên của Rick Hartley và cố gắng suy nghĩ về lời khuyên này trong ngữ cảnh. Thật không may, các khuyến nghị trong ghi chú ứng dụng không phải lúc nào cũng được coi là hạt muối và chúng thường được áp dụng trong những trường hợp không thể áp dụng được.

Bài viết này nói về thời điểm không sử dụng định tuyến trace trực giao, hơn là cách nó có thể được định cấu hình trong máy tính tự động hoặc một chủ đề tương tự. Nếu bạn đã làm việc trong thế giới tốc độ cực cao / tần số cao trong một thời gian dài, thì điều này rất có thể không phải là điều mới mẻ đối với bạn. Đối với phần còn lại của chúng ta, có một sự cám dỗ để mặc định thông tin cũ thường được cung cấp mà không có ngữ cảnh. Điều này đặc biệt đúng với định tuyến trace trực giao.

Stackups không hợp lệ dẫn đến định tuyến không hợp lệ

Tôi nghĩ rằng lần đầu tiên tôi thấy một khuyến nghị rằng các nhà thiết kế sử dụng định tuyến trực giao là trên StackExchange. Trang web này là một nguồn tài nguyên tuyệt vời về nhiều chủ đề, và nó chắc chắn là nguồn tài nguyên thường xuyên của tôi về tất cả những thứ liên quan đến phần mềm và mã hóa. Với thiết kế điện tử và PCB ngày càng trở nên phức tạp, có thể dễ dàng áp dụng các đề xuất từ trang web này và trang web khác mà không cần xem xét ngữ cảnh, dẫn đến các trường hợp các lựa chọn thiết kế này khiến bo mạch bị lỗi.

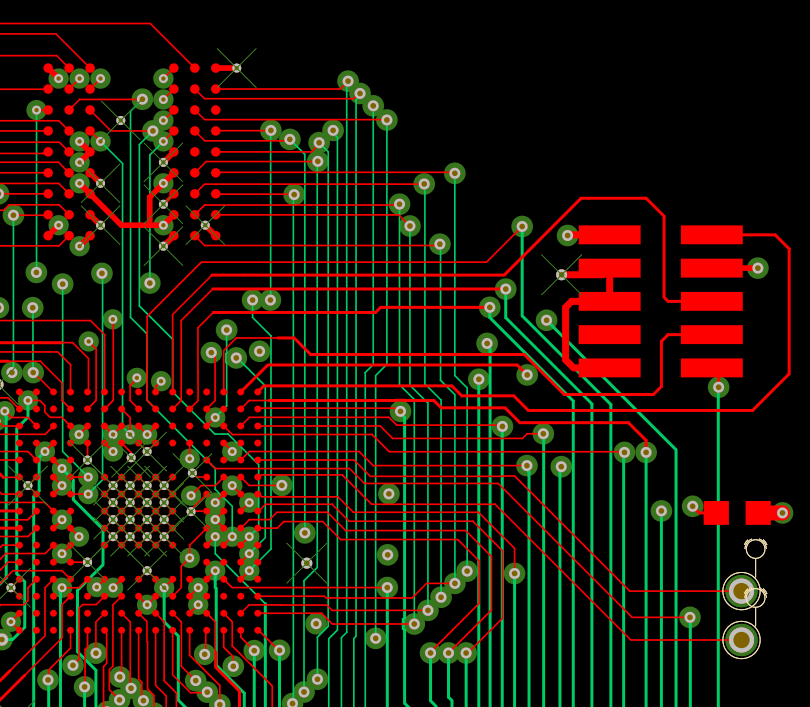

Gần đây tôi đã có một khách hàng đang tìm kiếm một số trợ giúp để gỡ lỗi nâng cấp cho một thiết kế cũ hơn. Khách hàng đã quyết định sử dụng đề xuất định tuyến trace trực giao cổ điển với lớp stack-up 6 lớp, tương tự như cách stack-up được hiển thị bên dưới. Trong stackup này, hai lớp trên cùng và hai lớp dưới cùng là các lớp tín hiệu. Các trace trong các lớp này được định tuyến trực giao giữa các IC và các vias xuyên lỗ tiêu chuẩn được sử dụng cho quá trình chuyển đổi lớp.

Không sử dụng cách stack-up 6 lớp đơn giản này với tín hiệu tốc độ cao

Nhà thiết kế có kinh nghiệm nên đã có ý tưởng về những gì sai sót trong bức tranh này. Vấn đề là kỹ sư đang cố gắng nâng cấp thiết kế để sử dụng MCU mới chạy ở tốc độ 400 MHz với các giao tiếp tốc độ cao nhưng không thay đổi stack-up, và thiết kế chắc chắn đã thất bại.

Tại thời điểm này, giải pháp nên rõ ràng; thiết kế stack-up đúng cách và bạn sẽ không phải dựa vào định tuyến trực giao để đảm bảo tính toàn vẹn của tín hiệu khi làm việc với tốc độ sườn cao (high edge rate). Hóa ra, đây rốt cuộc là một vấn đề về tính toàn vẹn nguồn, vấn đề này ít liên quan đến định tuyến trực giao mà liên quan nhiều hơn đến việc sắp xếp các lớp. Tuy nhiên, điều này đặt ra câu hỏi: khi nào bạn nên sử dụng định tuyến trực giao?

Khi nào thì áp dụng định tuyến trace trực giao?

Mục tiêu chính trong việc sử dụng định tuyến theo trace trực giao trên các lớp tín hiệu liền kề là loại bỏ nhiễu xuyên âm cảm ứng (inductive crosstalk) giữa các trace. Khi một tín hiệu số lan truyền, nó tạo ra một từ trường và các sườn chuyển đổi của tín hiệu sẽ tạo ra một từ thông thay đổi trong vùng xung quanh trace. Khi các đường sức từ tới trên một vòng dây dẫn kín vuông góc với diện tích vòng dây, từ thông thay đổi gây ra và quay trở lại EMF trong đường tín hiệu nạn nhân (cảm ơn bạn, Michael Faraday!).

Khi các kết nối trên các lớp liền kề được định tuyến trực giao (dọc theo các hướng vuông góc), từ trường từ một trace sẽ luôn được định hướng song song với vòng dây dẫn được hình thành bởi một trace nạn nhân trên lớp tiếp theo, loại bỏ hiệu quả nhiễu xuyên âm cảm ứng trực tiếp. Mặc dù mô tả này đúng về mặt kỹ thuật, nhưng nó quá đơn giản và không tính đến các khía sườn quan trọng khác của việc bố trí và stack-up PCB thực sự. Các vấn đề chính liên quan đến việc sử dụng định tuyến trực giao liên quan đến tốc độ chuyển mạch, decoupling và xác định một đường trở lại đáng tin cậy . Rick Hartley thảo luận về một số khía sườn định tuyến và stack-up quan trọng này trong một cuộc phỏng vấn gần đây .

Mặc dù có thể hạn chế khớp nối cảm ứng, nhưng vẫn có khớp nối điện dung, ngay cả với khu vực giao nhau nhỏ giữa các trace. Nếu bạn chưa thiết kế đúng đường trở lại của mình, điện trường giữa tín hiệu lớp 1 và mặt đất của nó (xem hình trên) có thể ghép nối trở lại với các tín hiệu trong lớp 2 chỉ đơn giản là do sự khác biệt tiềm ẩn trên điện dung lẫn nhau của chúng, tạo ra nhiễu xuyên âm điện dung. Trở kháng mà tín hiệu ghép điện dung nhìn thấy sẽ thấp hơn khi tốc độ sườn tín hiệu nhanh hơn, tạo ra xung dòng điện mạnh hơn trong trace nạn nhân.

Các thiết kế nâng cao như thế này sẽ không sử dụng định tuyến trace trực giao.

Ở tốc độ sườn thấp hơn, bạn có thể sẽ không nhận thấy nhiễu xuyên âm điện dung, bất kể định tuyến trực giao có được sử dụng hay không. Nó vẫn sẽ xảy ra, nhưng nó có thể không đủ lớn để vượt qua biên độ nhiễu của bất kỳ thành phần nào được kết nối với trace nạn nhân. Ở tốc độ thấp, các tín hiệu được ghép cảm ứng có trở kháng thấp hơn, do đó bạn muốn định tuyến trực giao trên các lớp tín hiệu liền kề để giảm thiểu ghép nối cảm ứng. Làm việc với tốc độ sườn thấp là một ví dụ khi định tuyến trace trực giao trong các lớp tín hiệu liền kề là thích hợp.

Đối với phần còn lại của chúng tôi, chúng tôi thường làm việc dưới nano giây về tốc độ sườn, yêu cầu che chắn / cách ly cẩn thận giữa các lớp tín hiệu, đường trở lại được thiết kế cẩn thận và phân phối nguồn siêu ổn định . Tất cả đều phụ thuộc vào việc thiết kế stack-up PCB phù hợp .

Parallel lines of high impedance can couple dV/dt and dI/dt according to the gap and loop impedances. So it can be L or C or both. Saturn PCB design exe helps compute crosstalk and impedances in nH/mm and pF/mm for RF which includes fast risetimes in logic.

More important for low EMI boards is orthogonal layouts permit easier connections with fewer vias.

https://www.nwengineeringllc.com/article/the-best-high-speed-board-design-guidelines.php

One important point I’d like to add; with high speed devices (e.g., rise times of less than 1 ns), it is not a good idea to use orthogonal routing. This routing recommendation is still spread on many forums and by some “design experts.” While this guideline may have been fine in years past, when digital devices tended to run much slower, this guideline should not be used in modern high speed PCBs. The idea behind orthogonal PCB trace routing is to eliminate inductive crosstalk. However, at high speeds, digital signal bandwidths reach into the GHz, and capacitive crosstalk between orthogonal traces will start to become noticeable. If you design the stackup correctly, then you won’t need to use orthogonal routing. I’ve discussed this in a recent article on Altium’s PCB design blog.