Nếu tôi là một siêu anh hùng, kryptonite của tôi sẽ dễ dàng khiến tôi không thể đến bất cứ đâu khi tôi mong đợi. Tôi luôn đi muộn ít nhất là năm phút, và tôi bắt đầu phải dành cho mình thêm gần hai mươi hoặc ba mươi phút nữa chỉ để bù đắp cho sự trễ giờ không thể tránh khỏi của mình. Gần đây, tôi đã thực sự bắt đầu cố ý đặt đồng hồ của mình về phía trước mười phút để giúp tôi đánh giá thời gian trung thực hơn.

Trong thiết kế PCB, bạn mong đợi các tín hiệu Clock đến kịp thời đến đích của mạch tích hợp (IC) của nó. Tuy nhiên, một hiện tượng được gọi là lệch xung nhịp có thể dẫn đến tín hiệu xung nhịp đến sớm hơn hoặc muộn hơn tại một số IC nhất định. Tất nhiên, điều này gây ra sự mâu thuẫn đối với tính toàn vẹn dữ liệu của các IC tương ứng.

Clock Skew là gì?

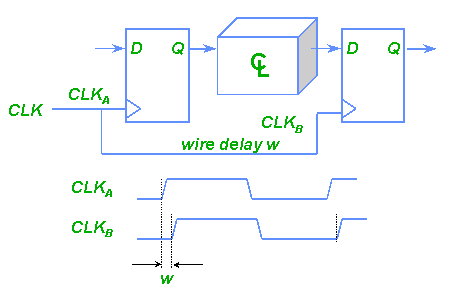

Độ lệch Clock là một hiện tượng trong đó các tín hiệu Clock đến các điểm đến khác nhau trong những khoảng thời gian khác nhau. Tín hiệu xung nhịp thường được sử dụng để giao tiếp đồng bộ trong thiết kế PCB. Ví dụ: Giao diện ngoại vi nối tiếp (SPI) sử dụng tín hiệu Clock để truyền và nhận dữ liệu giữa các thiết bị.

Trong cấu hình lý tưởng master đến các slave khác nhau, không có độ trễ trong thời gian truyền của tín hiệu Clock. Tất cả các linh kiện được kết nối trên bus xung nhịp dự kiến sẽ nhận được tín hiệu cùng một lúc.

Tuy nhiên, trong ứng dụng đời thực, độ trễ lan truyền xảy ra và xung Clock có thể đến các điểm đến trong khoảng thời gian khác nhau. Thủ phạm của hiện tượng lệch Clock là điện dung ký sinh và độ dài trace khác nhau của các tín hiệu Clock.

Hãy tưởng tượng một tín hiệu Clock bắt nguồn từ driver và chia thành hai con đường khác nhau. Đường dẫn A bằng một nửa chiều dài của đường dẫn B và cả hai đều kết nối với các máy thu khác nhau. Việc Clock báo hiệu trên Đường A đến đích sớm hơn tín hiệu Clock trên Đường B.

Sự khác biệt giữa thời gian đến của tín hiệu Clock và các chân nhận là giá trị skew.

Clock Skew ảnh hưởng đến PCB như thế nào

Trong thiết bị điện tử, tín hiệu xung nhịp đóng vai trò là tham chiếu thời gian để một thành phần chốt bit dữ liệu trên các hân nhận. Một số giao thức chốt dữ liệu trên một xung Clock hướng lên trong khi những giao thức khác làm như vậy trên một xung Clock hướng xuống. Bất kể cơ chế chốt là gì, một tham chiếu Clock đáng tin cậy là rất quan trọng.

Trong trường hợp clock skew, tín hiệu Clock có thể đến sớm hơn hoặc muộn hơn dự định. Khi Clock thay đổi trước khi cập nhật tín hiệu dữ liệu, thành phần nhận sẽ chốt dữ liệu cũ vào thanh ghi của nó. Nếu giao thức chốt dữ liệu dựa trên trạng thái ổn định của Clock thay vì chuyển đổi, thì hiện tượng lệch Clock có thể dẫn đến việc receiver ghi đè bộ nhớ bằng hai dữ liệu kết quả.

Nói chung, độ lệch Clock không phải là vấn đề với thiết kế tốc độ thấp vì có một biên độ sai số lớn. Tuy nhiên, nếu bạn đang thiết kế một ứng dụng tốc độ cao trong vùng hàng trăm MHz, thì độ lệch xung nhịp trở thành mối quan tâm thực sự.

Độ lệch Clock là một vấn đề quan trọng trong thiết kế tốc độ cao.

Lỗi chốt có thể dẫn đến hư hỏng nghiêm trọng về tính toàn vẹn của dữ liệu và điều đó có thể gây ra thảm họa trong các ứng dụng thực tế. Phòng bệnh hơn chữa bệnh khi trẻ mọc răng do lệch kim Clock.

Làm thế nào để Ngăn chặn Clock Skew trong Thiết kế PCB

Khi bạn đã hiểu rõ nguyên nhân Clock bị lệch thì việc ngăn chặn hiện tượng trở nên dễ dàng hơn. Chìa khóa để ngăn chặn sự lệch Clock nằm ở việc đảm bảo các tín hiệu Clock đến cùng một lúc trên các máy thu receiver khác nhau.

Để làm điều đó, bạn sẽ muốn đảm bảo rằng độ dài trace giữa đầu nguồn phát source và các điểm đến phải bằng nhau (độ dài phù hợp – length matching). Điều này có nghĩa là chiều dài trace ngắn nhất có thể không phải là con đường tốt nhất nữa.

Chiều dài trace bằng nhau giúp chống lệch Clock.

Trong một thiết kế đồng bộ điển hình, bạn sẽ có một driver được kết nối với một số receiver. Rất có thể, một số receiver sẽ gần driver hơn và một số receiver khác sẽ ở xa PCB hơn. Trước tiên, bạn sẽ muốn định tuyến tín hiệu Clock đến chân xa nhất và đảm bảo trace tín hiệu Clock khác được định tuyến với cùng độ dài.

Điều quan trọng là tránh các nhánh trong tín hiệu Clock để ngăn chặn sự phản xạ. Điều này có thể được thực hiện bằng cách sử dụng clock driver thay vì định tuyến trực tiếp từ thành phần source đến các receiver.

![]()

Ngoài ra, sử dụng điện trở nối tiếp gần phía driver (matching resistor) để phù hợp trở kháng trên tín hiệu Clock cũng giúp đảm bảo tính toàn vẹn của tín hiệu Clock.