Việc phân phối đồng đều các nguồn điện và ground cho các thiết bị khác nhau trên mạch là cần thiết để thiết kế mạng phân phối điện tốt. Điều mong muốn là có một mặt phẳng nguồn chuyên dụng cho mọi điện áp cần thiết.

Tổng số lượng net như vậy thường vượt quá số lớp có sẵn trong bảng mạch in stack up. Để giảm bớt khó khăn này, các nhà thiết kế thường xuyên tách các mặt phẳng sao cho nhiều mạng điện hoặc net ground có thể được định tuyến trên một lớp mặt phẳng tín hiệu duy nhất. Mặc dù mặt phẳng phân chia phân phối tốt các nguồn điện và net ground khác nhau nhưng nó cũng tạo ra một rào cản bổ sung đối với đường truyền tín hiệu trở lại. Do đó, các nhà thiết kế mặt phẳng phân chia phải đảm bảo rằng tất cả net nguồn và net ground được phân bổ đồng đều trong khi vẫn duy trì đường dẫn trở lại rõ ràng cần thiết cho các tín hiệu tốc độ cao nhạy cảm. Điều này đảm bảo bo mạch luôn hoạt động, đáp ứng yêu cầu PDN.

Giới thiệu

Trong những ngày đầu thiết kế Bảng mạch in (PCB), Mạng phân phối điện (PDN) không phải là một vấn đề nổi bật. Với thiết kế tốc độ cao phổ biến trong bối cảnh hiện tại, hiệu suất PDN phải được dự đoán sớm trong thiết kế PCB và được điều chỉnh để đáp ứng thông số kỹ thuật của thiết bị với điện áp thấp hơn, dòng điện cao hơn và biên độ nhiễu chặt chẽ hơn. Mục tiêu của PDN là cung cấp điện áp sạch và ổn định cho các thiết bị lõi trong thiết kế sản phẩm phức tạp.

Tuy nhiên, do các phần tử tạo nên mạng lưới nguồn có thêm các yếu tố ký sinh nên phân tích PDN không hoàn hảo. Nó có thể được sử dụng để đánh giá và giảm thiểu các vấn đề ở đường nguồn điện chính ở giai đoạn đầu của thiết kế. Hoạt động của PDN được ước tính bằng cách đo các tham số mức PCB như tổng trở kháng mạng tương ứng, điện trở DC và tổng độ tự cảm của vòng lặp. Để đạt được khả năng cung cấp điện năng đáng tin cậy và tổn thất điện năng thấp, tất cả các thiết kế PCB phải có trở kháng PDN gần bằng 0.

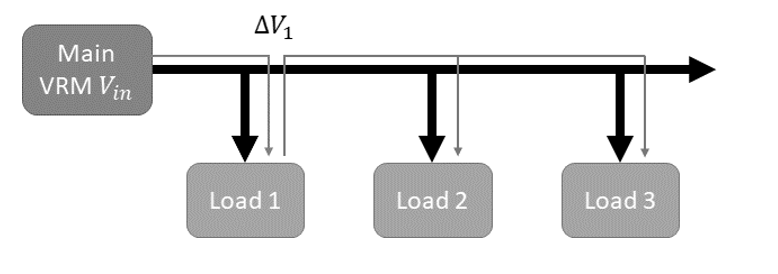

Đường nguồn điện trên PCB là một phần cấu trúc của PDN. Vì vậy, một tải nhất thời được tạo ra trên bất kỳ một tải nào cũng có thể ảnh hưởng trực tiếp đến đường nguồn và các tải khác có thể bị ảnh hưởng từ đó. Tải của Mô-đun ổn áp chính (VRM) được hiển thị trong Hình 1. Việc chuyển mạch ở Tải 1 gây ra nhiễu điện áp nhất thời và được lặp lại bởi các tải khác. Trong tình huống này, các bộ phận lấy một lượng lớn dòng điện từ đường nguồn điện tương ứng liên quan đến sự kiện chuyển mạch. Trong lượng dòng điện lớn này rút ra, nó sẽ tương tác với vật ký sinh PCB trên khắp mặt phẳng.

Nhiều mạch logic chuyển đổi cùng lúc trong một mạch tích hợp thực tế, dẫn đến dạng sóng kết hợp phức tạp như được đo trên đường nguồn điện.

Hình 1: Hiệu ứng nhất thời của PCB đối với tải

Cần một PDN tốt hơn

Các linh kiện hoạt động của PCB cần có năng lượng từ nguồn điện để hoạt động và một PDN tốt sẽ đáp ứng được nhu cầu này. Trên PCB, trước đây, các thiết bị mạch tích hợp thường chỉ có một chân nguồn và chân ground có thể dễ dàng liên kết với một đường dài. Khi mật độ mạch tăng lên, việc kết nối các mạch với nguồn điện và mặt phẳng đất trên bo mạch nhiều lớp trở nên khó khăn hơn. Khi số lượng chân cắm tăng lên và nhu cầu nguồn điện của IC ngày càng phức tạp hơn, các bảng mạch bắt đầu phải đối mặt với một số vấn đề sau:

Nhiễu điện từ (EMI): Mạch điện tử ngày càng dễ bị ảnh hưởng bởi EMI từ cả nguồn bên trong và bên ngoài khi tốc độ hoạt động của nó tăng lên. Điều chỉnh các mặt phẳng nguồn và ground giúp bảo vệ các nhiễu vào và ra để tránh các vấn đề EMI.

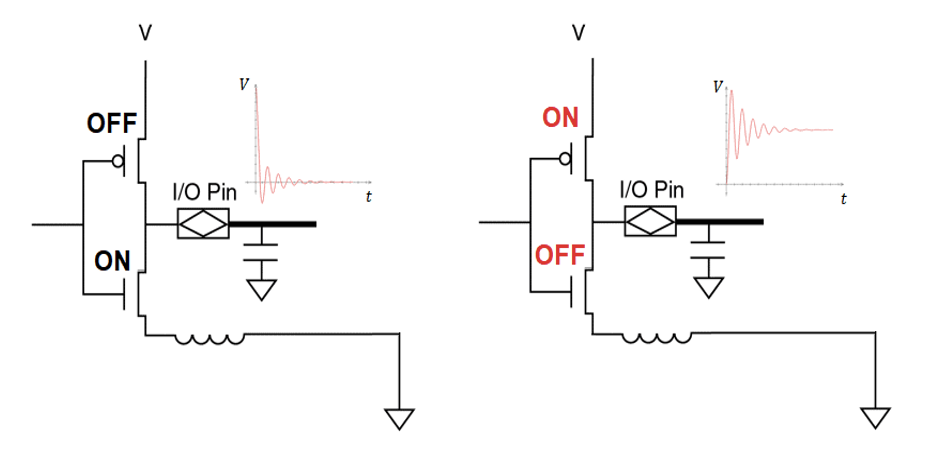

Ground bounce: Nhiễu chuyển đổi đồng thời, còn được gọi là dội đất, xảy ra khi một số lượng lớn tín hiệu số chuyển trạng thái cùng một lúc. Người ta quan sát thấy rằng trong các bus dữ liệu và bộ nhớ, nếu tín hiệu không quay trở lại mặt phẳng tham chiếu tương ứng do chuyển đổi nhanh, chúng sẽ có hiệu ứng dội ngược. Tác động này có thể gây ra nhiễu không mong muốn trong các mạch dẫn đến chuyển mạch nhầm khiến thiết bị gặp trục trặc. Khi dòng điện được kéo vào PDN, hiệu ứng điện áp nhất thời điển hình nhất là ground bounce. Khi điều này xảy ra, điện áp ground tham chiếu tăng lên trong khi đường nguồn dương trên PDN không đổi. Mức ground tham chiếu có thể được kiểm soát với sự trợ giúp của PDN được thiết kế tốt.

Power ripple (gợn): Khi dòng điện nhất thời lan truyền dao động điện áp trên đường nguồn dương, nó sẽ tạo ra nhiễu hoặc gợn sóng trong mạch điện. Đây không giống như tín hiệu đầu ra AC được chỉnh lưu. Những sóng này có thể gây ra nhiễu xuyên âm trong các mạch khác và làm giảm chất lượng tín hiệu trong các mạch đó. Tuyến dòng điện và các vật thể ký sinh có trong tuyến dòng chảy tách biệt hai tác động. Hình 2 cho thấy trường hợp sử dụng điển hình đối với ground bounce và gợn sóng của đường nguồn điện.

Hình 2: Ground bounce và gợn sóng điện

Mạch tích hợp (IC) có nhiều kết nối nguồn và ground hơn để xử lý, ngoài ra còn có tốc độ chuyển mạch nhanh hơn của các mạch dòng điện. Trên một chip xử lý lớn có package Ball-Grid Array (BGA), có hàng trăm chân nguồn và chân ground với các giá trị tham chiếu khác nhau. Để cấp nguồn cho bộ xử lý, các chân này cũng có thể tiêu thụ rất nhiều dòng điện. Do đó, việc đảm bảo nguồn điện không bị nhiễu, gợn sóng và nhiễu đòi hỏi phải có PDN được thiết kế tốt.

Thông tin cơ bản về PDN

PDN có thể được biểu diễn dưới dạng mạng RLC và giống như bất kỳ mạch điện nào có điện trở nào đó, nó có thể hiển thị phản hồi nhất thời đại diện cho dao động tắt dần. Trở kháng PDN (Z) có thể được biểu thị bằng sự kết hợp của điện trở, điện cảm và điện dung (RLC).

- Cuộn cảm: Z = jωL

- Tụ điện: Z = 1/(jωC)

- Điện trở: Z = R

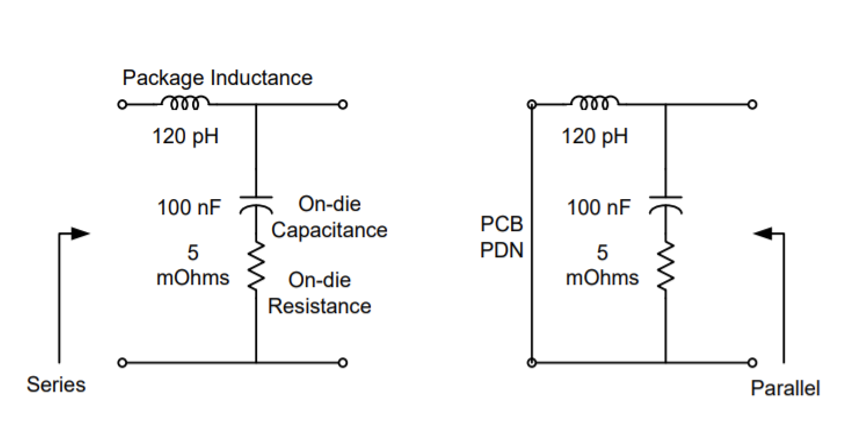

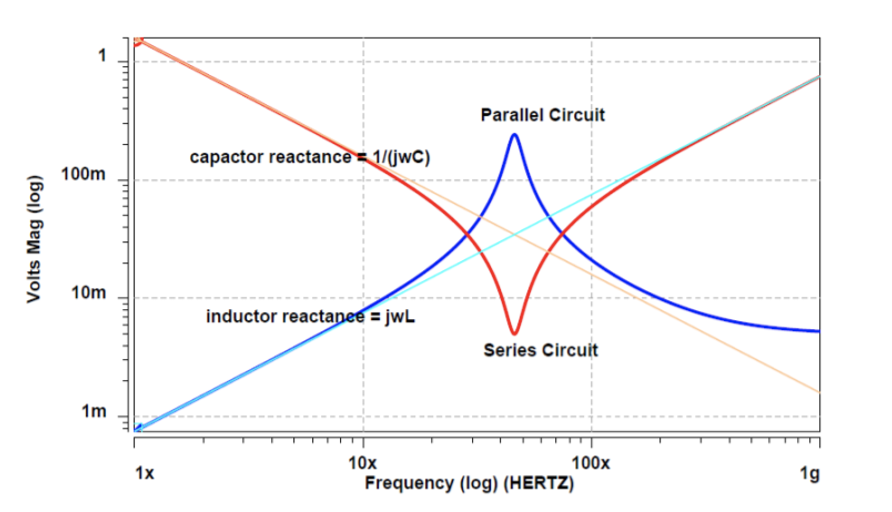

Hình 3: Thành phần RLC cho PCB PDN

Hình 3 cho thấy các thành phần RLC của PCB PDN. Độ phức tạp của các cấu trúc die (thiết bị bóng bán dẫn hiệu ứng trường (FET), khuếch tán, v.v.) có thể được kết hợp với độ phức tạp của các cấu trúc gói (vias, mặt phẳng công suất, ball, v.v.) và được biểu thị bằng chuỗi đơn giản và mạch song song cho mục đích cộng hưởng. Các mạch RLC nối tiếp từ góc độ đo lường thành phần (nhìn từ bên ngoài). Tuy nhiên, do PCB PDN có trở kháng rất thấp nên điện dung On-Die (ODC) song song với độ tự cảm của package từ trong ra ngoài (nhìn từ trong ra ngoài). Khi các thành phần mạch giống nhau được mắc nối tiếp và song song, chúng sẽ hoạt động khác nhau. Đáp ứng tần số của mạch RLC nối tiếp và song song điển hình được thể hiện trên Hình 4.

Hình 4: Đáp ứng tần số cho RLC nối tiếp và song song

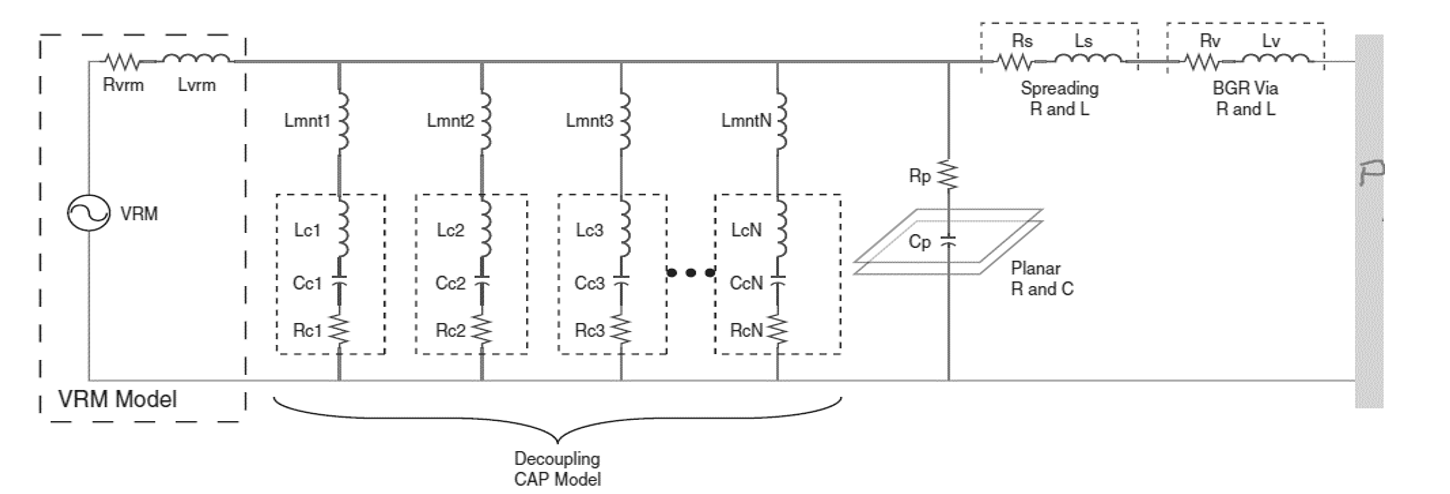

Giờ đây, trace đồng cho chân nguồn và mặt phẳng đồng cho chân ground cũng đóng một vai trò quan trọng trong hiệu suất PDN. Một mô hình PDN đơn giản hóa có thể được hiển thị trong hình 5.

Hình 5: Mô hình PDN đơn giản hóa

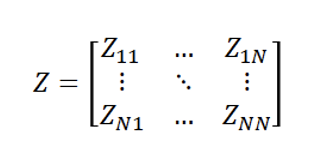

PDN giống như một mạng đa cổng. Thành phần chuyển mạch trên xe buýt DC có thể ảnh hưởng đến việc phân phối điện tổng thể của xe buýt DC. Nó có thể gây ra một số biến đổi về nguồn DC được cảm nhận bởi tất cả các thành phần trên PDN. Trong mô phỏng, các tham số Z được sử dụng để đánh giá mối quan hệ giữa các trở kháng nhìn thấy ở các cổng khác nhau. Sự dao động điện áp nhìn thấy được tại cổng PDN liên quan đến dòng điện chạy vào tất cả các cổng PDN được xác định bởi ma trận tham số này.

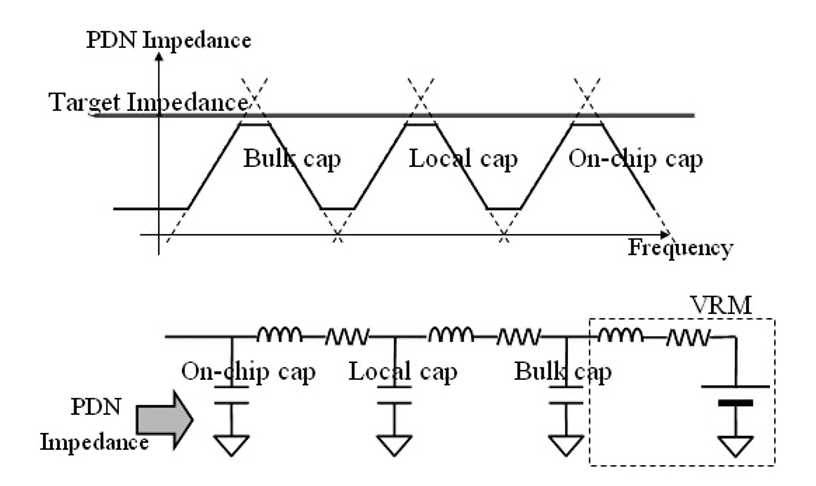

Trở kháng mục tiêu/tối đa cho phép (PDN) đặt giới hạn cho giá trị trở kháng tối đa cho phép đối với PDN. Dạng sóng gợn sóng nhất thời trên đường dây điện được xác định bởi trở kháng PDN chuyển đổi thành jitter cho IC tốc độ cao. Để chuyển mạch IC, nó lấy dòng điện từ các bus nguồn đại diện cho dạng sóng xung thông qua PDN. Bất kỳ tụ điện và/hoặc điện dung ký sinh nào trong PDN sẽ tạo ra một số điện kháng, dẫn đến phản ứng nhất thời trong PDN. Mục đích của việc điều khiển trở kháng PDN là giảm thiểu ảnh hưởng của bất kỳ dạng sóng nhất thời nào.

Hình 6: Mục tiêu trở kháng PDN

Mục tiêu là giữ phổ mục tiêu ở dưới giá trị trở kháng mục tiêu, từ DC đến tần số mục tiêu. Phương pháp Miền tần số được sử dụng để tính toán Trở kháng mục tiêu. Do ưu thế của điện cảm trải phẳng ký sinh và điện cảm gói, việc thêm một số lượng tụ điện decoupling hợp lý sẽ không làm giảm trở kháng đường nguồn điện |ZEFF| dưới trở kháng mục tiêu (ZTARGET).

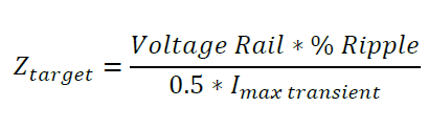

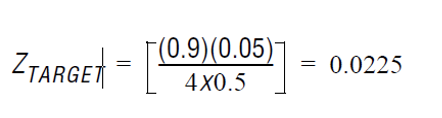

Ví dụ: để tách hiệu quả đường nguồn 0.9 V, FTARGET 50 MHz, độ gợn 5% (Thành phần AC) và dòng điện tối đa cho phép là 4A (coi 50% là dòng điện nhất thời) ZTARGET có thể được ước tính như sau:

PDN sử dụng các tụ điện (decoupling), điện dung giữa các mặt phẳng và độ tự cảm để cung cấp cấu hình trở kháng rất thấp (Zeff) dưới trở kháng mục tiêu (ZTARGET) cho đến tần số mong muốn.

Sự thay đổi điện áp trên bus nguồn là do trở kháng PDN cao. Phương pháp tốt nhất là giảm trở kháng PDN xuống mức thấp nhất có thể đạt được. Điều này được thực hiện bằng cách lựa chọn cẩn thận các tụ điện decoupling và sắp xếp một cách có chiến lược các nguồn điện hoặc ground lân cận để đạt được điện dung giữa các mặt phẳng cao.

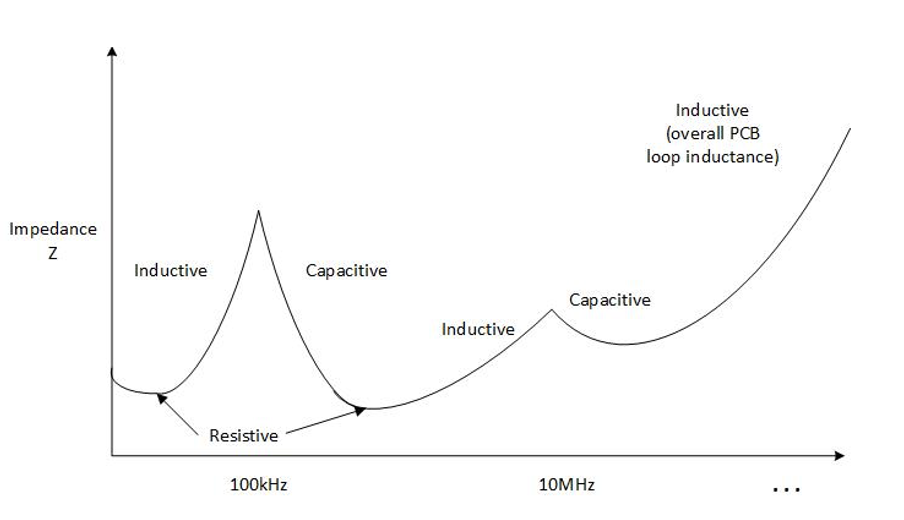

Trở kháng PDN và dòng điện nhất thời xác định lượng dạng sóng gợn sóng nhất thời trên bus PDN. Vì trở kháng có thể được mô tả là miền chức năng của tần số, nên đường cong trở kháng phải nằm dưới giá trị mục tiêu/đỉnh đã đặt trên băng thông tín hiệu tương ứng. Mối quan hệ này có thể được bắt nguồn từ định luật Ohm. Hình 7 cho thấy một đường cong điển hình của trở kháng theo tần số.

Hình 7: Đường cong trở kháng và tần số điển hình

Phân tích PDN

Để trích xuất hiệu suất PDN của bố cục PCB, người ta có thể cần những thông tin sau làm đầu vào:

- Sơ đồ thiết kế

- Stack-up PCB có đặc tính điện môi (Dk và Df)

- Bố cục layout PCB

- Thông số S của tụ điện từ nhà sản xuất

- Công cụ toàn vẹn nguồn điện

Trở kháng PDN có thể bị ảnh hưởng bởi nhiều yếu tố khác nhau, bao gồm cấu trúc PCB và sự ký sinh PCB trong các phần tử của mạch điện. Điều này có thể được đánh giá thêm từ hai góc độ – phần mềm mô phỏng mạch và field solver.

A. Phương pháp EM-Field Solver

Field Solver đặt các điều kiện biên trên trường điện từ thay vì các đặc tính của mạch và giải trực tiếp phương trình Maxwell. Việc xây dựng ma trận tham số Z cho cấu trúc PDN và ước tính trở kháng của PDN nhiều cổng tiềm năng bằng các kết quả này là khả thi. Trở kháng PDN có thể được biểu diễn dưới dạng ma trận trở kháng với các tham số Z:

Hình 8: Ma trận trở kháng

Đối với mạng cổng N, trở kháng PDN có thể được xác định theo ma trận tham số Z. Các số hạng đường chéo biểu thị trở kháng tự và các số hạng ngoài đường chéo biểu thị trở kháng truyền. Trở kháng truyền giải thích cách dòng điện được đưa vào một cổng gây ra nhiễu điện áp cho tất cả các cổng khác trong PDN, trong khi đó trở kháng tự hoặc trở kháng đặc tính định lượng nhiễu điện xảy ra tại một cổng trong PDN do dòng điện được đưa vào cùng một cổng.

Để giải quyết vấn đề này và tính toán ma trận trở kháng PDN được hiển thị ở trên, hãy áp dụng công cụ giải trường điện từ 3D chấp nhận dữ liệu trực tiếp từ bố cục PCB. Phương pháp mô phỏng này là phương pháp nhanh nhất để tính toán trở kháng PDN với một số bus công suất và các nhánh của chúng, nhưng lại tốn thời gian cho việc thiết kế mạng tách rời cho PDN.

B. Mô phỏng mạch điện

Mô phỏng mạch không thể tính đến tất cả các ký sinh trong tính toán trở kháng PDN do cấu trúc phức tạp của PDN thực tế trừ khi chúng được đặt làm các thành phần mạch có thể so sánh được. Tuy nhiên, có thể sử dụng một loạt tụ tách gắn vào PDN để tạo ra điện áp DC nhất quán để mô phỏng phổ trở kháng. Người ta có thể thực hiện quét tham số trên mạng tụ điện có chứa điện cảm ký sinh trong các mô hình tụ điện bằng cách sử dụng công cụ mô phỏng SPICE trong các công cụ thiết kế sơ đồ. Mục đích là để thử nghiệm các giá trị và số lượng tụ điện khác nhau để tìm ra cấu hình tụ điện lý tưởng giúp giảm thiểu trở kháng PDN.

Bước đầu tiên trong việc đánh giá và điều chỉnh trở kháng PDN là sử dụng mô phỏng mạch. Bởi vì trở kháng dao động theo tần số nên việc tính toán phổ trở kháng từ DC đến tần số rất cao là mục tiêu của bạn trong việc kiểm soát trở kháng PDN. Trở kháng PDN phải đủ để đáp ứng băng thông tín hiệu mà các bộ phận của bạn yêu cầu. Trong mô phỏng mạch, điều này đòi hỏi phải xem xét các yếu tố sau:

Tụ điện tự cộng hưởng: Do Điện trở nối tiếp tương đương (ESR) và Độ tự cảm nối tiếp tương đương (ESI), các tụ điện decoupling hoặc bypass trên mọi thành phần đều có một số tần số tự cộng hưởng. Bảng dữ liệu có thể được sử dụng để thu được các giá trị điển hình cho tần số tự cộng hưởng của các tụ điện được chọn.

Điện dung giữa các mặt phẳng: Điện dung giữa ground và mặt phẳng nguồn của PDN của bạn được xác định bằng cách stack up PCB. Cần phải xác minh rằng PDN trong PCB thiết kế tốc độ cao có khả năng tách rời thích hợp ─ đây là hiệu ứng ký sinh. Có thể giảm thiểu sự phụ thuộc vào các tụ điện decoupling/bypass rời rạc bằng cách tận dụng điện dung vốn có khi stack up. Đối với PCB 6 lớp có độ dày tiêu chuẩn, giá trị điển hình là 0,5 pF/sq. mm.

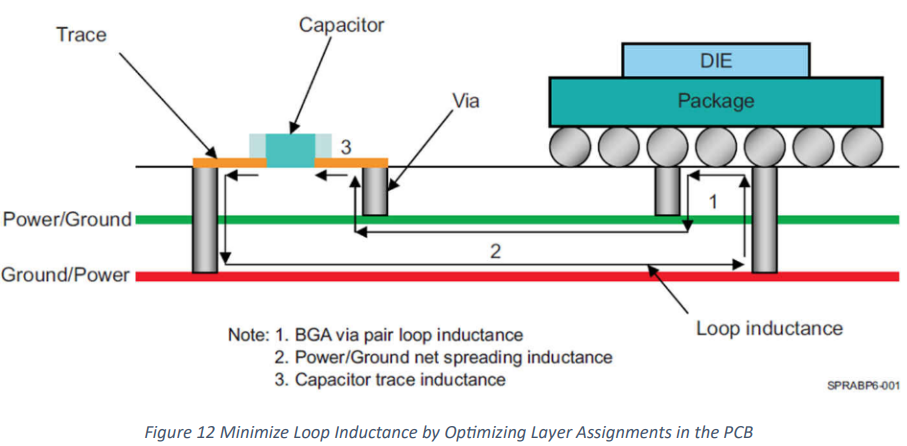

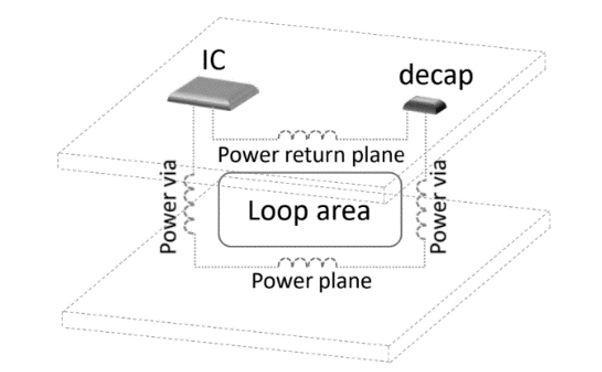

Điều quan trọng cần nhớ là có một số thứ mà mô phỏng mạch không thể đánh giá được. Cần xem xét ký sinh trùng trong các tụ điện như ESL và ESR. Điện dung giữa các mặt phẳng và các ký sinh trùng khác không thể được tính toán một cách rõ ràng. Thay vào đó, hãy tính đến bất kỳ phần ký sinh nào trong thiết kế dưới dạng các phần mạch tương đương. Điều này đòi hỏi phải ước tính điện dung phẳng và độ tự cảm của vòng lặp mặt phẳng. Hình 9 mô tả sự hình thành của độ tự cảm vòng lặp điển hình.

Hình 9: Hình ảnh độ tự cảm của vòng lặp

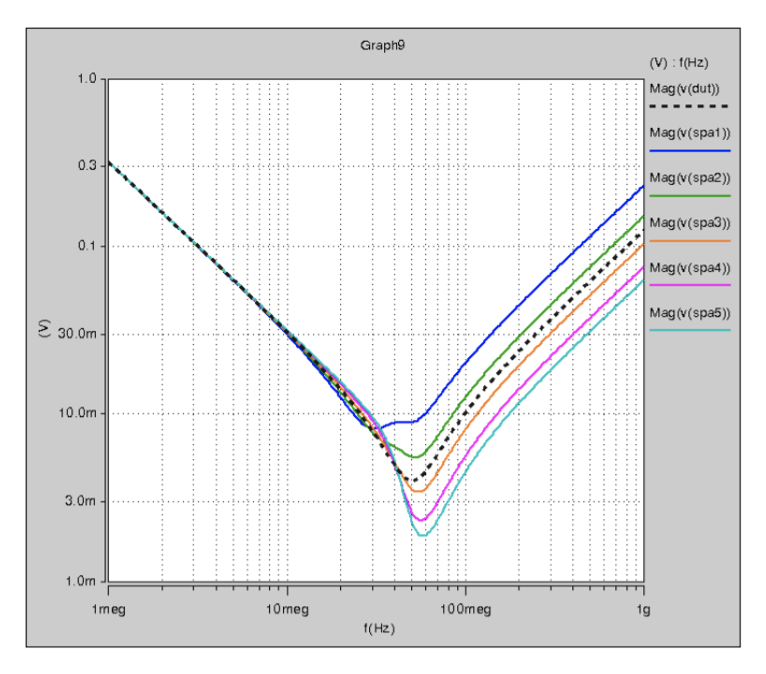

Hành vi PDN ở mỗi tần số có thể là điện trở, điện cảm hoặc điện dung. Nó là sự kết hợp của cộng hưởng nối tiếp và song song. Biểu đồ mô phỏng Spice điển hình được trình bày trong Hình 10.

Hình 10: Mô phỏng Spice

Một số công cụ tiêu chuẩn ngành để thực hiện phân tích là phân tích giảm DC, phân tích tách AC, Tính toàn vẹn nguồn và tối ưu hóa PDN HyperLynx, Trình phân tích PDN, Công cụ PDN và Allegro Sigrity. Một số công cụ trực tuyến được sử dụng để tính toán trở kháng là CircuitLab và PDN Tool.

Hướng dẫn thiết kế PCB cho PDN

Việc đạt được trở kháng mục tiêu PDN có thể khó khăn. Sử dụng các nguyên tắc được đề cập bên dưới, bạn có thể đạt được PDN gần với giá trị mục tiêu.

- Luôn điều chỉnh các lớp stack up một cách đối xứng (tức là các lớp trên cùng phải được nhân đôi ở các lớp dưới cùng). Sự kết hợp của các lớp stack up không đồng đều, nhiệt độ và áp suất cao trong quá trình sản xuất có thể khiến bo mạch bị biến dạng.

- Các lớp Prepreg và Core có độ dày đối xứng nhau (trong cấu trúc của stack up).

- Chỉ định các lớp nguồn và ground trước tiên và càng gần nhau càng tốt, tức là độ dày điện môi tối thiểu giữa mặt phẳng nguồn và ground.

- Nếu có thể, hãy giữ cho các lớp nguồn và mặt phẳng ground trong stack up lớp bảng mạch đối xứng nhau để duy trì tính toàn vẹn của tín hiệu.

- Cố gắng duy trì các lớp đồng có mật độ cao nhất ở giữa stack up. Một lần nữa, điều này phải được thực hiện kết hợp với các quy trình đảm bảo tính toàn vẹn tín hiệu thích hợp.

- Đối với các lớp mặt phẳng khác nhau, sử dụng cùng trọng lượng đồng. Cân nhắc sử dụng chất độn kim loại (đổ đồng) ở những nơi không có nhiều kim loại.

- Điều quan trọng nhất, trước khi cam kết stack up lớp bo mạch được đề xuất, hãy xác minh với nhà sản xuất PCB để đảm bảo rằng quy trình đó có thể chế tạo được nó.

- Xác nhận với nhà chế tạo khoảng trống Anti-pad (khu vực trống xung quanh lớp mặt phẳng bên trong) tối thiểu mà anh ta có thể thực hiện một cách đáng tin cậy. Thực hiện theo thiết kế tương tự vì nó giúp giảm điện trở DC.

- Việc lập kế hoạch phân bố các vùng PCB phải được ưu tiên cao nhất và phải được xem xét và thực hiện trong khi schematic được hoàn thành 50-60%. Bạn có thể tăng tốc quá trình bằng cách tận dụng thiết kế tham chiếu ngay từ đầu.

- Sử dụng tụ điện decoupling sau khi đặt thành phần chính. Điện cảm là kẻ thù ở đây và điện dung là cứu cánh. Số lượng tụ điện càng cao thì số lỗi trong PDN càng ít.

- Chọn nhiều giá trị tụ điện khác nhau để cấu hình trở kháng thu được của chúng phẳng và trông có điện trở ở mọi tần số.

- Via on pad nên được tuân theo bất cứ nơi nào có thể trong thiết kế. Không chỉ dành cho fanout BGA mà còn dành cho cả các ứng dụng khác. Tránh chia sẻ via, nó có thể là thảm họa.

- Vị trí và hướng của các tụ decoupling có thể được tối ưu hóa bằng cách kết hợp các vị trí đặt tụ điện ở mặt trên hoặc mặt sau.

- Không chia sẻ trace nguồn cho mạng gây nhiễu – kiểm tra nguyên tắc thiết kế và danh sách kiểm tra bố cục tương ứng với thiết bị.

- Vòng loop nguồn lớn hơn làm tăng độ tự cảm trong đường dẫn, tránh tạo đường dẫn điện cảm thông qua các vòng loop.

- Sử dụng càng nhiều đường dẫn trở lại song song trong các kết nối nguồn-ground.

- Mỗi chân nguồn điện phải có tụ decoupling. Kết nối chúng với via xuyên lỗ nếu ở phía bên kia của bảng mạch.

- Kết nối các net cùng tên với via. Via mù và via chôn nên được so le.

- Các mặt phẳng đồng có thể được sử dụng để cải thiện nhiệt.

- Tạo các plane cho đường nguồn, nếu không thể thì nên làm theo các đường rộng hơn tùy thuộc vào yêu cầu dòng điện ước tính.

- Chiến lược fanout phải được lên kế hoạch để tối ưu đường trở về và do đó độ tự cảm của vòng lặp có thể giảm.

- Đặt các via xuyên lỗ through-hole ở bốn góc của IC để tạo đường trở về dễ dàng.

- Để giảm đáp ứng điện áp đối với bước dòng điện thoáng qua, hãy tăng điện dung hoặc giảm độ tự cảm.

Phần kết luận

Việc đáp ứng các thông số kỹ thuật trở kháng PDN đảm bảo khả năng xảy ra lỗi ở mức tối thiểu hoặc gần như bằng 0 do sự cố PDN đối với tất cả các thiết bị trong mọi điều kiện hoạt động. Việc không đáp ứng các thông số kỹ thuật của PCB Z không có nghĩa là mọi thiết bị đều sẽ gặp lỗi. Điều đó có nghĩa là đối với sản xuất hàng loạt, số lượng hoạt động trong phạm vi điện áp và nhiệt độ hợp lệ được quy định kỹ thuật của thiết bị cho phép, xác suất hỏng hóc của một số phần trăm thiết bị không phải bằng 0.

Bất kể topology nào, người ta nên hướng tới việc thiết kế trở kháng PDN khả thi thấp nhất trong phạm vi băng thông mong muốn bằng cách sử dụng các nguyên tắc thiết kế. Trở kháng PDN sẽ không bao giờ bằng 0, mặc dù nó được dự đoán sẽ đạt giá trị milliOhm ở tần số GHz. Việc sử dụng nhiều tụ điện decoupling với các giá trị ESL khác nhau và các mặt phẳng lân cận hỗ trợ duy trì trở kháng PDN thấp, giúp hạn chế sự dao động điện áp bus nguồn và jitter trên tín hiệu đầu ra ở mức tối thiểu. Với nhiều tiêu chí thiết kế giúp tạo ra một PDN thành công, việc có các quy tắc thiết kế mạnh mẽ và hệ thống quản lý ràng buộc cũng rất có lợi.