Được xuất bản với sự cho phép của Flame Boss , nhà sản xuất bộ điều khiển hút thịt hậu mãi.

Trong nghiên cứu điển hình này, chúng ta sẽ xem xét một số nguy cơ của việc giảm chi phí bảng mạch của bạn về hiệu suất tương thích điện từ (EMC).

Đối tượng là một thiết kế 4 lớp ban đầu đã vượt qua thử nghiệm EMC, sau đó được giảm xuống thành thiết kế 2 lớp và sau đó không thành công. Chúng ta sẽ đi vào những phát hiện chính của đánh giá thiết kế EMC ban đầu mà tôi đã thực hiện trên thiết kế 4 lớp, sau đó đi vào những thay đổi cần thiết để vượt qua bảng 2 lớp.

Đây là những gì chúng ta sẽ đề cập:

- Những phát hiện chính của đánh giá thiết kế EMC của bảng mạch 4 lớp (Sau đó được thông qua tại phòng thí nghiệm EMC)

- Giảm chi phí từ 4 lớp xuống 2 lớp và dẫn đến lỗi EMC

- Chiến lược tôi sử dụng để xác định và khắc phục sự cố phát xạ từ xa

- Những phát hiện chính của đánh giá thiết kế EMC lần thứ hai của PCB 2 lớp

- Nguyên tắc: Cách tối ưu hóa thiết kế 2 lớp để có hiệu suất xạ thải thấp

Máy hút khói BBQ Flame Boss Wi-Fi

Năm ngoái, Roger Collins, chủ sở hữu của Flame Boss , đã yêu cầu tôi thực hiện đánh giá thiết kế EMC cho thiết bị điều khiển nhiệt độ gọn gàng của anh ấy trước khi gửi nó đến nhà thử nghiệm.

Sản phẩm kết nối với máy xông khói hoặc BBQ để theo dõi nhiệt độ không khí và thịt và quạt gió điều khiển chính xác cấu hình nhiệt độ.

Nó thay thế nhiệm vụ trông nom người hút thuốc hàng giờ để đảm bảo bạn có được miếng thịt ngon ngọt. Nó thậm chí còn được tích hợp Wi-Fi để bạn có thể theo dõi mọi thứ từ xa.

Mô tả và kết quả đánh giá thiết kế EMC ban đầu

Mặc dù các bộ phận bên trong của thiết bị này không có tốc độ đặc biệt cao (như chúng ta sẽ tìm hiểu bên dưới), nhưng vẫn có nhiều khả năng xảy ra lỗi phát xạ dẫn hoặc bức xạ tại phòng thử nghiệm.

Tôi đã thấy các sản phẩm 25 MHz đơn giản không đạt yêu cầu kiểm tra phát xạ bức xạ. Như chúng ta sẽ thấy bên dưới, việc vượt qua bài kiểm tra sẽ trở nên khó khăn hơn nhiều khi bạn bị hạn chế làm việc trên 2 lớp.

PCB 4 lớp gốc

BỐ CỤC PCB 4 LỚP GỐC

Ảnh chụp màn hình này hiển thị bố cục PCB 4 lớp ban đầu. IC chính là MCU dòng NXP MK12DX (lõi ARM) chạy ở tần số mặc định là 20,48 MHz. Không siêu nhanh, nhưng cũng không siêu chậm. Dù sao thì tốc độ quay (cạnh) mới quan trọng hơn.

Sản phẩm có 4 cổng kết nối với cáp bên ngoài:

- Cổng J-IN: Đầu vào 12V DC (ở trên cùng bên trái)

- Cổng J-FAN: Tín hiệu điều khiển động cơ quạt PWM

- Cổng J-T1/T2: Cảm biến nhiệt độ cho không khí/thịt

Và 2 cổng kết nối nội bộ:

- J_LCD: Giao diện LCD 8 bit

- J-BUT: Nhập nút từ bàn phím

Về phát xạ bức xạ, tôi quan tâm nhiều hơn đến các cổng kết nối với hệ thống cáp bên ngoài. Ở tốc độ xung nhịp liên quan đến thiết kế này, các chế độ lỗi phát xạ bức xạ có nhiều khả năng hơn là do các dòng điện ở chế độ chung tìm đường thoát ra các cáp bên ngoài.

Tiêu chuẩn EMC cho sản phẩm

Sản phẩm được dành để bán cho khách hàng cuối cùng, những người có thể sẽ sử dụng nó trong môi trường dân cư. Điều đó có nghĩa là nó sẽ tuân theo các giới hạn phát xạ dẫn và bức xạ ‘loại B’ nghiêm ngặt hơn – mức phát thải thấp hơn khoảng 10dB so với ‘loại A’ được phép dưới 1 GHz.

Điều này chỉ có nghĩa là việc vượt qua các thử nghiệm phát xạ bức xạ và tiến hành có thể khó khăn hơn một chút, vì vậy chúng ta nên nỗ lực hơn nữa vào các phương pháp hay nhất về thiết kế EMC.

Bản gốc Đánh giá Thiết kế EMC Quan sát & Phát hiện

Do thiết kế này tương đối không bị hạn chế về không gian và có 4 lớp để sử dụng nên việc tối ưu hóa thiết kế để có hiệu suất phát thải tốt không phải là một vấn đề lớn.

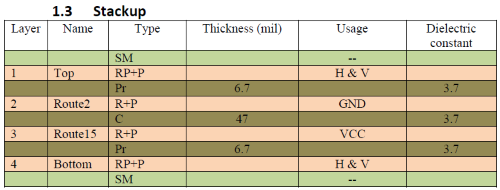

STACK-UP PCB 4 LỚP GỐC FLAME BOSS

Một nơi tốt để bắt đầu đánh giá thiết kế EMC là nền tảng thiết kế của bạn – stack-up PCB. Vì vậy, đây là nơi đầu tiên tôi tìm kiếm.

Trong thiết kế này, Flame Boss đã sử dụng stack-up PCB điển hình được đề xuất cho các bo mạch 4 lớp, đó là định tuyến/linh kiện ở lớp trên cùng và lớp dưới cùng, với hai lớp ở giữa dành riêng cho plane nguồn và plane đất.

Như bạn có thể thấy từ kích thước độ dày trong bảng trên, các lớp định tuyến được liên kết chặt chẽ với nhau, với phần Core (C) dày (47 mil) giữa các lớp GND và VCC.

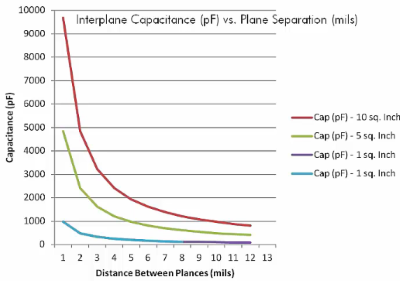

Từ góc độ EMC, lý tưởng nhất là các lớp PWR/GND được liên kết chặt chẽ để tăng điện dung giữa các mặt phẳng plane nguồn và GND. Điều đó làm tăng khả năng cung cấp dòng điện ở tần số rất cao của mặt phẳng để đáp ứng bất kỳ nhu cầu nào của IC.

Nhưng trên bảng 4 lớp, thông thường tốt hơn là hy sinh điện dung giữa các mặt phẳng tăng lên để giảm thiểu các khu vực vòng lặp đường dẫn trở lại và thay vào đó làm cho độ rộng của trace được kiểm soát trở kháng mỏng hơn.

NGUỒN SẠC TRÊN CHÂN NGUỒN IC VỚI NHU CẦU DÒNG ĐIỆN TẠM THỜI [NGUỒN: EMC DÀNH CHO NHÀ THIẾT KẾ PCB (K. ARMSTRONG)]

Ngoài ra, điện dung giữa các mặt phẳng trên một bảng mạch nhỏ như thế này không lớn (như bạn có thể thấy từ sơ đồ này) và thực sự sẽ chỉ có hiệu quả trong việc cung cấp dòng điện trong vài trăm pico giây đầu tiên trước khi dòng điện từ các tụ decoupling cục bộ có thể đảm nhiệm.

Vì vậy, stack-up có vẻ tốt.

6 mục tiêu để có một stack-up PCB tốt

Nếu bạn muốn đánh giá stack-up PCB của riêng mình từ góc độ EMC, đây là 6 điều lý tưởng mà bạn muốn có. [Nguồn: Kỹ thuật Tương thích EMC, Ott].

1. Các lớp tín hiệu kề mặt phẳng

Chúng tôi muốn các lớp tín hiệu (định tuyến) luôn liền kề với ít nhất một mặt phẳng (PWR hoặc GND). Điều đó thực hiện ít nhất 2 điều đối với chúng ta về mặt điện từ:

(a) Nó cho phép chúng tôi kiểm soát chính xác trở kháng, nếu được điều chỉnh đúng cách, sẽ giảm thiểu phản xạ và tối ưu hóa tính toàn vẹn của tín hiệu và

(b) Điều đó có nghĩa là dòng điện trở về ở gần nhất có thể với dòng điện truyền đi. Điều đó giảm thiểu diện tích vòng lặp dòng điện chế độ vi sai (DM) và do đó giảm thiểu phát xạ bức xạ do dòng điện DM.

Để có công cụ miễn phí tính toán trở kháng tín hiệu (và nhiều thông số khác), hãy xem bộ công cụ PCB tuyệt vời từ Saturn PCB.

2. Các lớp tín hiệu liên kết chặt với mặt phẳng

Lý tưởng nhất là các lớp tín hiệu cũng được liên kết chặt chẽ với mặt phẳng liền kề (trái ngược với liên kết lỏng lẻo). Điều này giúp với một vài điều:

- Giảm thiểu khu vực vòng lặp dòng điện bao gồm các đường dẫn gửi và nhận vì đường dẫn trở về gần về mặt vật lý

- Khi trace và mặt phẳng di chuyển gần nhau hơn, độ tự cảm của mặt đất giảm (giảm điện áp rơi trong mặt phẳng đối với một dòng điện nhất định)

Những yếu tố này trong hầu hết các trường hợp dẫn đến giảm phát xạ bức xạ và nhiễu xuyên âm giữa các trace liền kề.

3. Các mặt phẳng PWR + GND được ghép nối chặt chẽ (tăng điện dung giữa các mặt phẳng)

Chúng tôi muốn các lớp năng lượng và mặt đất liền kề và rất gần nhau. Như tôi đã đề cập ở trên, điều này làm tăng điện dung giữa các mặt phẳng, cho phép lưu trữ nhiều năng lượng hơn. Vì các mặt phẳng có độ tự cảm thấp nhất so với bất kỳ nguồn năng lượng nào trên bo mạch của bạn trong mạng phân phối điện PDN, nên chúng là nguồn năng lượng đầu tiên và tốt nhất cho nhu cầu dòng điện tức thời từ các chân nguồn IC.

4. Tín hiệu tốc độ cao trên các lớp bên trong (để chứa trường điện tử + tín hiệu quan trọng che chắn)

Lý tưởng nhất là chúng tôi muốn các tín hiệu tốc độ cao, hay cụ thể hơn là các tín hiệu có tốc độ quay nhanh được kẹp giữa hai mặt phẳng, giúp chứa trường điện từ và giảm nhiễu xuyên âm.

5. Nhiều mặt phẳng GND (để giảm điện cảm đường dẫn trở lại)

Cuối cùng, lý tưởng nhất là chúng tôi muốn có nhiều hơn một mặt phẳng mặt đất. Miễn là các mặt phẳng được liên kết rất tốt với nhau bằng các via stitching, điều này sẽ giúp giảm độ tự cảm của mặt phẳng mặt đất. Điều này sẽ giúp giữ cho nhiễu trên mặt đất thấp hơn (nhiễu điện áp thấp hơn sẽ được phát triển đối với một lượng dòng nhiễu nhất định). Điều này có nghĩa là ít nhiễu hơn được truyền vào hệ thống cáp bên ngoài mà chúng tôi biết là nguồn EMI tiềm năng chính.

6. Các tín hiệu quan trọng được định tuyến trên tối đa 2 lớp và được tham chiếu đến cùng một mặt phẳng

Nếu bạn cần định tuyến các tín hiệu quan trọng trên nhiều lớp, bạn nên sử dụng tối đa hai lớp và chúng phải được tham chiếu đến cùng một mặt phẳng. Lý do cho điều này là để đảm bảo rằng khu vực vòng lặp đường dẫn trở lại hiện tại được giảm thiểu. Nếu tín hiệu không được tham chiếu đến cùng một mặt phẳng (như trong ví dụ hiển thị bên phải ở đây), dòng điện trở lại phải tìm cách đi từ mặt phẳng này sang mặt phẳng khác (trong trường hợp này, mặt dưới của mặt phẳng nguồn đến mặt trên của mặt phẳng GND).

Nếu bạn không cung cấp một tuyến đường gần đó cho dòng điện trở lại đó, chẳng hạn như tụ điện decoupling nằm ngay bên cạnh tín hiệu đi qua, thì bạn có nguy cơ tạo ra một vòng lặp dòng điện lớn. Các vòng lặp dòng điện lớn = ăng-ten có khả năng phát xạ tốt, vì vậy chúng tôi muốn tránh trường hợp đó.

Thỏa hiệp và ưu tiên

Nếu bạn có thể đáp ứng một số hoặc hầu hết các mục tiêu đó, thì bạn sẽ làm tốt hơn rất nhiều nhà sản xuất phần cứng ngoài kia. Nghiêm túc mà nói, trong nhiều năm thực hiện đánh giá thiết kế EMC, tôi đã bắt gặp rất nhiều bảng mạch mà nhà thiết kế thậm chí không chỉ định độ dày của lớp và trong một số trường hợp cũng không chỉ định thứ tự lớp. Vì vậy, về cơ bản, họ sẽ làm việc với các trở kháng không xác định trên bo mạch của họ, nghĩa là tính toàn vẹn của tín hiệu là không xác định.

Không thể đáp ứng tất cả 6 tiêu chí này với bất kỳ bảng mạch nào ít hơn 8 lớp, vì vậy đối với bảng mạch 4 lớp như thế này, chúng ta cần thực hiện một số đánh đổi có học thức.

Nếu bạn đang tìm kiếm một số hướng dẫn ở đây, thì tôi khuyên rằng hai mục tiêu đầu tiên là quan trọng nhất, vì vậy tôi luôn khuyên bạn nên triển khai hai mục tiêu này.

Những mục tiêu này cũng có nghĩa là điều quan trọng là phải có cuộc đối thoại với nhà sản xuất PCB của bạn để đảm bảo rằng họ có thể đáp ứng stack-up mà bạn muốn. Thường có một chút trao đổi qua lại với nhà sản xuất để xem độ dày lõi Core và Prepreg tiêu chuẩn của họ là bao nhiêu, sau đó bạn có thể bắt đầu và tính toán kích thước độ rộng trace và khoảng cách dựa trên thông tin đó để đạt được trở kháng mà bạn muốn.

Danh sách các khuyến nghị cải thiện EMC/EMI

Quay lại đánh giá thiết kế EMC 4 lớp.

Mặc dù thiết kế có thể đã vượt qua thử nghiệm phát xạ mà không có bất kỳ thay đổi nào, nhưng đánh giá thiết kế EMC là cơ hội để cải thiện hiệu suất điện từ và loại bỏ rủi ro đối với quy trình chứng nhận.

Các mục chính tôi khuyên bạn nên thay đổi trong thiết kế 4 lớp ban đầu là:

- Cải thiện việc decoupling trong một số khu vực cụ thể

- Tối ưu hóa khả năng decoupling bằng cách cải thiện hướng tụ decoupling và khoảng cách via

- Tăng chiều rộng trace của một số đường nguồn cung cấp điện để giảm trở kháng PDN (và giảm nhiễu của nguồn điện)

- Thêm ferrite bead cho đường nguồn cung cấp tương tự và đường nguồn cung cấp RF

- Định tuyến lại một số phần của bảng mạch để giảm thiểu các trace ở mặt sau của PCB

- Hoán đổi chân giao tiếp với LCD trên MCU để truyền tín hiệu đến đầu nối connector mà không cần nhảy lớp

- Thêm các điện trở nối tiếp trên một số tín hiệu giao tiếp nối tiếp để thêm giới hạn slew rate và yêu cầu termination. Hoặc ít nhất là đặt các điện trở 0 ohm để sử dụng làm dự phòng khi cần thiết

- Thêm một số vị trí linh kiện không hàn cho bộ lọc thông thấp RC trên mỗi tín hiệu chuyển sang LCD

- Giảm cường độ điều khiển trên tất cả các tín hiệu được điều khiển từ MCU khi băng thông cho phép

- Thêm via stitching GND trên bảng mạhc cứ sau 10 mm-20 mm để giảm khả năng xảy ra cộng hưởng mặt phẳng plane

- Sử dụng cáp có bọc shield cho quạt PWM

- Khuyến nghị thêm điốt bảo vệ ESD vào tín hiệu đầu dò nhiệt độ càng gần đầu nối càng tốt

- Thêm bộ lọc thông thấp (RC đơn giản) với băng thông thấp (ví dụ: 500 Hz) vào đầu vào tương tự. Điều này bảo vệ chống lại các trường bức xạ ghép nối với cáp khỏi thử nghiệm EMC miễn nhiễm bức xạ (61000-4-3).

- Một số mục khác mà tôi sẽ không đề cập ở đây để giảm thiểu một số thử nghiệm miễn nhiễm EMC khác.

Cập nhật thiết kế 4 lớp

Dựa trên đánh giá ban đầu, Roger đã sửa đổi PCB để cải thiện hiệu suất EMC/EMI trước lịch trình thử nghiệm cuối cùng.

CẬP NHẬT BỐ CỤC PCB 4 LỚP

Các lớp mặt phẳng GND và PWR cho phép chúng ta định tuyến các tín hiệu vuông góc với nhau ở các lớp trên cùng và dưới cùng mà không phải lo lắng quá nhiều về việc cắt các đường dẫn dòng điện trở lại.

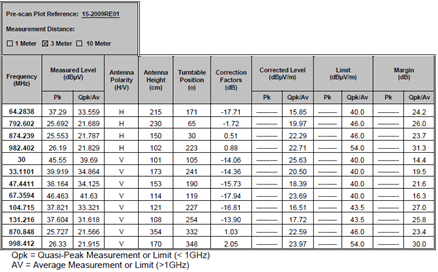

DỮ LIỆU “PASS” VỀ PHÁT THẢI BỨC XẠ BAN ĐẦU

Theo dữ liệu thử nghiệm từ phòng thí nghiệm EMC, mức phát xạ trong trường hợp xấu nhất là 14,4 dB dưới giới hạn (ở 30 MHz). Đó là sự chênh lệch lớn, vì vậy đó là một kết quả rất tốt.

Giảm chi phí từ 4 đến 2 lớp

Vài tháng sau, Roger quyết định giảm bớt bảng mạch và một trong những khu vực chính để tiết kiệm tiền là trên chính bảng mạch trần.

Tùy thuộc vào số lượng đặt hàng, điều này có thể thể hiện khoản tiết kiệm 50c – $2 cho mỗi đơn vị [dựa trên báo giá trực tuyến nhanh], giúp tăng nhanh chóng cho các thiết bị tiêu dùng số lượng lớn.

Đây là bảng mới được cô đọng thành 2 lớp.

GIẢM XUỐNG 2 LỚP PCB

Những gì chúng ta có thể thấy là vì các lớp bên trong đã biến mất nên chúng ta mất rất nhiều tùy chọn định tuyến. Do đó, bạn có thể thấy nhiều trace hơn được định tuyến ở mặt dưới của PCB, bao gồm cả trace nguồn và dữ liệu. Điều này có nhược điểm đáng kể là biến mặt phẳng mặt đất (và các đường quay trở lại khác) thành pho mát Thụy Sĩ.

Mọi thứ đột nhiên trông không được đẹp lắm và từ những gì tôi thấy về thiết kế mới, tôi ngay lập tức nghi ngờ rằng có thể có một số vấn đề về đường dẫn trở lại đã được đưa ra.

Quá trình quét phát xạ tương ứng từ phòng thử nghiệm cho thấy một số vấn đề khá lớn đã xuất hiện trên khắp dải tần 30 MHz – 500 MHz.

Theo hồ sơ phát xạ (tần số, băng thông, công suất, v.v.), có vẻ như chúng tôi có 2 vấn đề riêng biệt trở lên cần giải quyết.

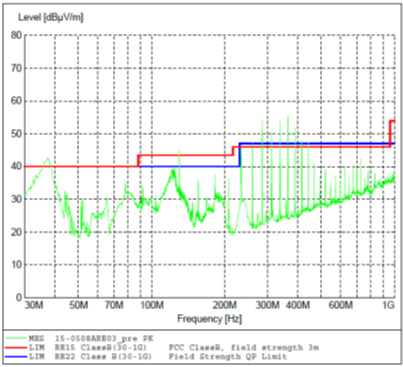

THẤT BẠI PHÁT XẠ BỨC XẠ

Phân tích sơ đồ phát thải bức xạ

Không có sẵn thiết bị vật lý để khắc phục sự cố tại phòng thí nghiệm tại nhà của mình, tôi cần phải thực hiện bằng cách đưa ra những phỏng đoán có cơ sở về nguồn phát xạ.

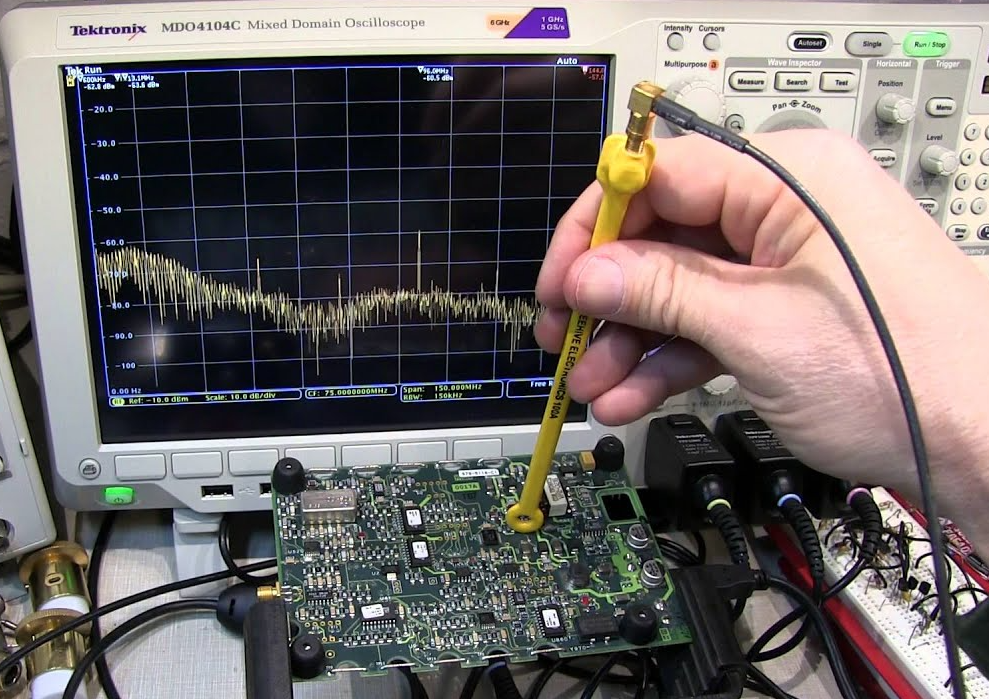

Tại phòng thí nghiệm EMC hoặc có sẵn thiết bị khắc phục sự cố/trước khi đi test, bạn có thể xác nhận nguồn rất nhanh bằng cách bật/tắt các khu vực của mạch điện, ngắt kết nối cáp và/hoặc dò tìm xung quanh bằng đầu dò trường gần (near field probe).

May mắn thay, chỉ dựa trên tần số và cấu hình của phát xạ liên quan, cùng với các bản sao của sơ đồ và layout PCB, tôi có thể mạo hiểm phỏng đoán một số nguồn nhiễu, cơ chế ghép nối và cấu trúc ăng-ten gây ra.

Bump ở 30-40 MHz

Với tần số tương đối thấp, băng thông rộng ‘va chạm’ như tần số bạn có thể thấy trong khoảng 30-40 MHz, tôi thường nghi ngờ những thứ như mạch điều khiển động cơ hoặc mạch cấp nguồn chuyển đổi.

Ngược lại, các tín hiệu rất lặp lại như tín hiệu số và clock có xu hướng rất hẹp vì tần số, slew rate, duty cycle không thay đổi nhiều.

Chúng tôi có một mạch PWM trên bo mạch để điều khiển động cơ quạt, vì vậy tôi nghi ngờ có thể có điều gì đó không ổn trong đường điều khiển ở đây.

Nhiễu băng thông rộng khoảng 120 MHz

Một lần nữa, tôi sẽ tìm kiếm bất cứ thứ gì về cơ- điện trước. Tôi nhận thấy rằng cũng có một buzzer áp điện trong thiết kế, theo lý thuyết nên được ‘bật’ cho mục đích thử nghiệm. Các phòng thử nghiệm luôn muốn đo lường tình huống xấu nhất, điều đó có nghĩa là mọi khu vực trong mạch của bạn phải hoạt động.

Một lần nữa, đây có thể không phải là vấn đề, nhưng bản chất băng thông rộng của phát xạ khiến tôi phải xem xét cẩn thận các đường điều khiển cho cả mạch điều khiển động cơ và mạch buzzer. Với một bộ dò trường gần hoặc GTEM nhỏ, bạn có thể tìm ra nó khá nhanh, nhưng tôi không có bảng mạch trong tay để xác nhận.

Ngoài ra, các loại va chạm này có thể là các nguồn tần số thay đổi khác, chẳng hạn như clock, thiết bị được điều khiển bằng PWM hoặc thậm chí là tín hiệu bức xạ có chủ ý được điều chế. Thiết kế chỉ có một bộ phát 2,4 GHz, vì vậy tôi đã loại trừ điều đó vì những va chạm này có tần số thấp hơn nhiều.

Phát xạ băng hẹp ở 100-200 MHz

Các ‘gai’ băng thông hẹp như thế này trong dải tần số này thường là sóng hài của tần số clock hiện diện ở đâu đó trên sản phẩm. Nó có thể là clock của bộ xử lý chính hoặc đồng hồ lõi bên trong (thường là PLL lên đến bội số của tần số tinh thể bên ngoài) hoặc bus clock (ví dụ: tần số chuyển đổi bus dữ liệu song song/nối tiếp).

Trong trường hợp này, các xung được đặt cách nhau chính xác bằng tần số của clock bộ xử lý, vì vậy chúng tôi nghi ngờ rằng đó là nhiễu từ bộ xử lý được phát ra thông qua một số cơ chế.

Trong những trường hợp ít phổ biến hơn, các xung băng hẹp ở đây có thể được coi là sóng hài rất cao từ nguồn cung cấp switching được thiết kế kém. Nhưng với tần số SMPS ở vùng KHz/MHz thấp, tôi thường cho rằng các vấn đề về nhiễu sẽ giảm xuống dưới 50 MHz và thường dưới 30 MHz trong vùng thử nghiệm phát xạ được tiến hành.

Phát xạ ở 200-500 MHz

Các gai hẹp cách nhau khoảng 26 MHz ở tần số cao hơn cũng có vẻ là sóng hài từ clock trong thiết bị. Điều này rất có thể liên quan đến cùng một vấn đề phát xạ của bộ xử lý, vì vậy tôi thầm tin rằng nếu chúng ta giải quyết được vấn đề đó, các sóng hài này cũng sẽ giảm biên độ.

Nhìn chung, bạn có thể thấy rằng thiết bị bị lỗi ở một số tần số ở bất kỳ đâu trong khoảng từ 1 đến 7 dB.

Sửa đổi 2 lớp

Tôi đã trò chuyện với Roger và thảo luận về ý tưởng quay lại thiết kế 4 lớp vì không có gì đảm bảo rằng tôi có thể cải thiện thiết kế 2 lớp đủ để vượt qua thử nghiệm phát xạ. Nhưng dù sao thì anh ấy cũng muốn thử, vì vậy chúng tôi đã tiến hành cải thiện layout PCB 2 lớp.

Thay vì xem qua thiết kế và tạo báo cáo cho anh ấy, đó là điều tôi thường làm để đánh giá thiết kế, chúng tôi quyết định sẽ nhanh hơn nếu tôi chỉ thực hiện mọi thứ rồi cung cấp danh sách thay đổi sau đó. Điều này đã tăng tốc độ quay vòng chỉ còn 1 ngày.

Kết quả là bảng dưới đây:

ĐÃ CẬP NHẬT PCB 2 LỚP (SAU KHI XEM XÉT THIẾT KẾ EMC)

Những gì bạn có thể nhận thấy là hiện tại có ít trace hơn ở mặt sau của PCB. Ý tưởng đằng sau điều này là:

- Để giảm thiểu độ tự cảm của mặt đất bằng cách làm cho mặt phẳng đất càng lớn và liền kề càng tốt

- Để giảm thiểu việc tạo ra các vòng lặp dòng điện không chủ ý trong các đường dẫn trở lại

Dưới đây là một số thay đổi tôi đã thực hiện:

- Đã thêm tụ decoupling bổ sung ở đầu vào nguồn điện

- Định tuyến lại các trace xung quanh mô-đun RF để tránh các trace trên lớp đất càng nhiều càng tốt

- Đã thêm các tụ decoupling ở một số vị trí dọc theo đường nguồn chính để duy trì PDN trở kháng thấp và cung cấp đường dẫn ngắn hơn để dòng nhiễu quay trở lại nguồn của chúng

- Đã di chuyển đầu nối JTAG lớn ở góc trên bên phải của PCB gần hơn với MCU để giảm thiểu chiều dài trace và cung cấp thêm không gian định tuyến trên lớp trên cùng

- Hợp nhất các ground analog/số và nguồn điện analog/số. Trong trường hợp này, việc tách biệt nguồn cung cấp/nền kỹ thuật số và tương tự thực sự làm cho hiệu suất kém hơn vì các trace bổ sung gây ra một số vấn đề về đường dẫn trở lại

- Các trace nguồn được ưu tiên ở lớp trên cùng. Một trong những khu vực rủi ro cao nhất là đường dẫn điện được định tuyến ở phía dưới bên phải qua các tín hiệu dữ liệu LCD.

- Đã di chuyển một số linh kiện để làm cho các trace trôi chảy hơn trên lớp trên cùng

- Đã chuẩn hóa một số giá trị tụ điện decoupling thành 100 nF để tránh tạo cộng hưởng trong PDN

- Đã thêm tụ decouling bên cạnh chân nguồn LCD

- Một số tinh chỉnh nhỏ khác…

Hầu hết công việc là di chuyển các bộ phận và định tuyến lại để tránh các trace ở mặt dưới của PCB càng nhiều càng tốt để mặt phẳng tiếp đất có thể tiếp tục và các đường quay trở lại không bị gián đoạn.

Tôi cũng đã cải thiện việc decoupling ở một số khu vực và định tuyến lại nguồn cung cấp VCC chính để cố gắng giảm độ tự cảm/trở kháng của nguồn điện.

Mặc dù không được hiển thị ở đây, nhưng tôi cũng khuyên bạn nên thêm các điện trở nối tiếp (phần giữ chỗ 0 ohm hoặc 10-30 ohm) gần MCU cho tất cả các tín hiệu điều khiển được định sẵn để chuyển sang màn hình LCD. Điều này giống như cung cấp cho bạn một vị trí dự phòng để hàn linh kiện nếu giao tiếp LCD là có vấn đề từ góc độ phát xạ bức xạ.

Một cách dự phòng tốt khác là thêm các tụ điện X2Y trên vỏ động cơ quạt và trên PCB bên cạnh đầu nối động cơ. Nếu có khả năng quạt gây ra bất kỳ thành phần nào của nhiễu (ví dụ: xung 30-40 MHz hoặc xung 120 MHz), thì các tụ X2Y này có thể cực kỳ hiệu quả trong việc tách các dòng nhiễu.

Kết quả

VƯỢT QUA PHÁT XẠ BỨC XẠ 2 LỚP

Sau khi bo mạch được sản xuất lại với những thay đổi này (và một số thay đổi khác mà Roger đã sử dụng để hoàn thiện thiết kế), lượng phát xạ đã giảm đáng kể như bạn có thể thấy ở trên.

Các va chạm băng thông rộng ở 30-50 MHz và ~120 MHz đã giảm 5-10 dB.

Và nhiễu băng thông hẹp liên quan đến MCU đã biến mất bên dưới mức nhiễu của máy phân tích.

Rượu rum và coca ở khắp mọi nơi!

Tài nguyên khác:

KHÓA ĐÀO TẠO TRỰC TUYẾN: EMC DESIGN FOR COMPLIANCE (22 GIỜ)

HỘI THẢO TRÊN WEB ĐƯỢC GHI LẠI: BẮT ĐẦU ĐẾN KẾT THÚC ĐÁNH GIÁ THIẾT KẾ EMC (2 GIỜ)

SÁCH ĐIỆN TỬ: THIẾT KẾ EMC NGAY LẦN ĐẦU TIÊN

Quy tắc ngón tay cái cho thiết kế 2 lớp

Nếu bạn đang cân nhắc sử dụng bảng 2 lớp thay vì 4 lớp, đây là một số nguyên tắc chung để giảm thiểu rủi ro gặp phải một ngày tồi tệ:

- Chỉ định một lớp đầy đủ cho GND nếu có thể.

- Bị ám ảnh về việc giảm thiểu các linh kiện và định tuyến trên lớp GND để giảm thiểu sự phá vỡ trong các đường dẫn trở lại

- Đặt các linh kiện và đầu nối connector sao cho giảm thiểu các trace chồng chéo (làm giảm sự cần thiết của các trace đi trên lớp GND)

- Sử dụng vùng GND trên lớp trên cùng và thường xuyên đóng via vào lớp GND. Bằng cách đó, các dòng điện stray có thể ‘nhảy’ lên lớp trên cùng thay vì tạo ra các vòng lớn xung quanh các trace trên lớp GND

- Ưu tiên cho đường trace nguồn và định tuyến chúng trên một lớp càng nhiều càng tốt

- Thêm các tụ decoupling vào đường nguồn theo định kỳ để giảm thiểu các khu vực vòng lặp dòng điện nhiễu dẫn và duy trì trở kháng nguồn điện thấp

Phần kết luận

Vì vậy, như bạn có thể thấy, việc giảm chi phí PCB của bạn có thể dẫn đến một số thách thức về EMC. Bạn nên gán một yếu tố rủi ro cho ngân sách và thời hạn của mình nếu bạn chọn hy sinh một số mục tiêu mà chúng ta vừa nói đến. Việc giải quyết EMI ở cấp độ PCB thường rẻ hơn so với cấp độ vỏ bọc hoặc thậm chí tệ hơn là bạn phải trả tiền cho khách hàng trả lại nếu hiệu suất thực sự kém.

Dịch từ: https://emcfastpass.com/emc-cost-reduction/?fbclid=IwAR0tPo8Plr7mZpykJRNen3B8qvbDld-64YqE7uaZLb4RlYOS830d48uzPik