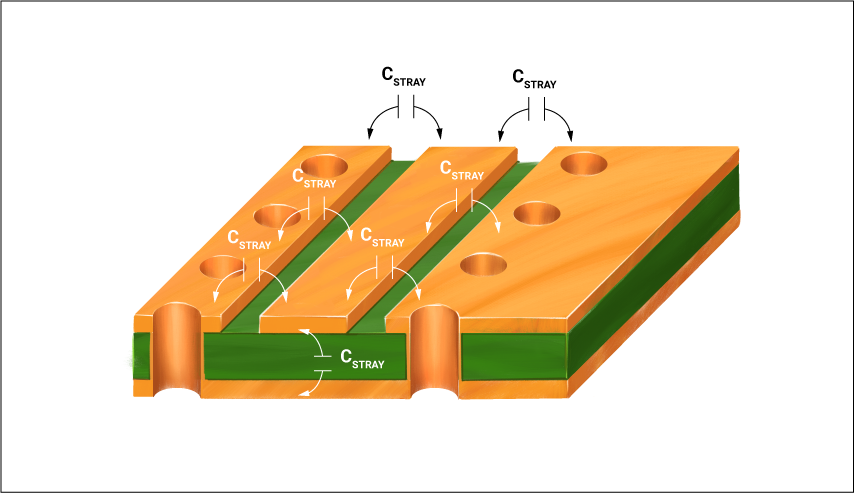

PCB bao gồm một số dây dẫn được kéo dài song song, ví dụ như các trace, được ngăn cách bởi một chất cách điện. Những trace này cùng với vật liệu điện môi tạo thành tụ điện, dẫn đến hiệu ứng điện dung ký sinh không mong muốn hoặc điện dung tạp tán.

Các yếu tố ký sinh trong PCB có thể là điện dung ký sinh, điện trở ký sinh và điện cảm ký sinh. Hiệu ứng điện dung ký sinh nổi bật trong bảng mạch tần số cao khi các trace được đặt gần nhau. Hiệu ứng này hoàn toàn không mong muốn và ảnh hưởng đến chức năng của thiết bị. Nó dẫn đến các vấn đề như nhiễu xuyên âm, EMI và tính toàn vẹn của tín hiệu. Các nhà thiết kế PCB xử lý tần số cao, tốc độ dữ liệu cao và các bảng mạch tín hiệu hỗn hợp phải xem xét các hiệu ứng điện dung và điện cảm ký sinh trong khi thiết kế layout PCB.

Điện dung ký sinh trong PCB là gì?

Các dây dẫn PCB được đặt gần nhau tạo thành một tụ điện ảo, dẫn đến hiệu ứng điện dung ký sinh.

Điện dung ký sinh hoặc điện dung tạp tán là kết quả của một tụ điện ảo được hình thành giữa hai trace được ngăn cách bởi một chất điện môi. Nó xảy ra do sự khác biệt tiềm năng được tạo ra khi các trace mang dòng điện chạy gần nhau.

Hiệu ứng này thậm chí có thể xảy ra nếu các dây dẫn được cách điện thích hợp. Không thể tránh được điện dung ký sinh vì không có mạch điện nào là lý tưởng.

Điện dung ký sinh được tính như thế nào?

Chu kỳ phóng/nạp của tụ điện.

Điện dung ký sinh là đặc tính cố hữu của vật dẫn điện. Nó là sự lưu trữ trên một đơn vị sự thay đổi của điện thế. Điện dung ký sinh được tính là C = q/v. Trong đó C là điện dung tính bằng farads, v là điện áp tính bằng vôn và q là điện tích tính bằng coulom.

- Đối với tín hiệu điện không đổi không thay đổi theo thời gian, dv/dt = 0 có nghĩa là không thay đổi điện thế; do đó i = 0.

- Nếu có một tụ điện trong vòng lặp mạch, dv/dt sẽ hội tụ về một giá trị cố định, tức là điện thế thay đổi, dẫn đến một dòng điện thay đổi; do đó i ≠ 0.

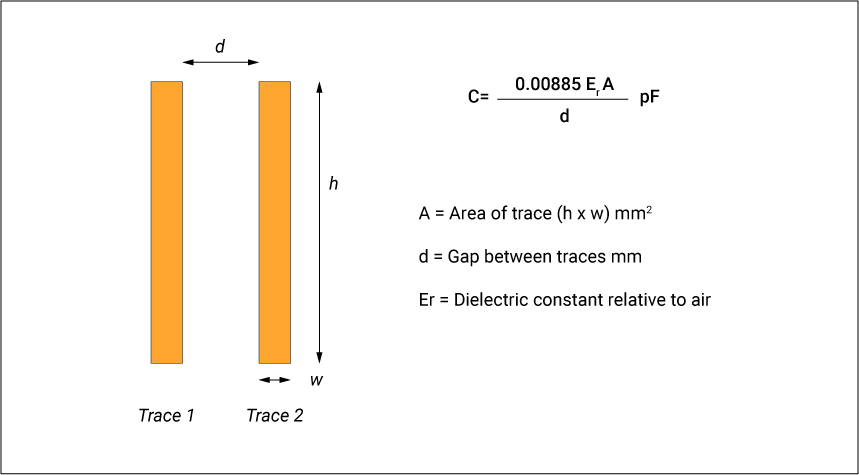

TÍNH TOÁN ĐIỆN DUNG THEO TRACE

Điện dung của một tụ điện hai bản song song được cho bởi công thức C = (kA /11.3d) pF. Trong đó C là điện dung, A là diện tích bản tính bằng cm2, k là hằng số điện môi tương đối của vật liệu làm bảng mạch và d là khoảng cách giữa các bản tính bằng cm.

Tính toán điện dung theo trace

Tính toán điện dung theo trace

Hiệu ứng điện dung ký sinh là gì?

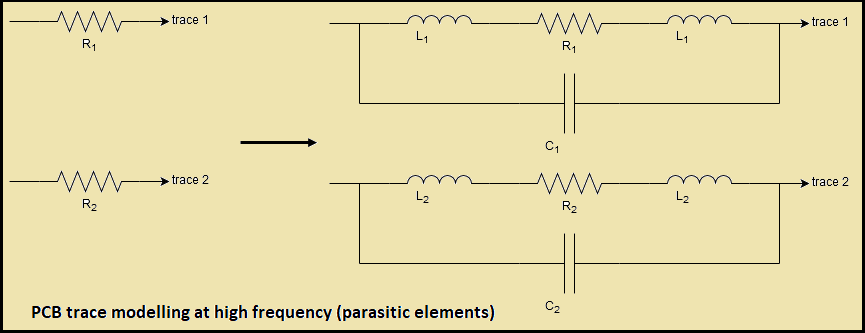

Mô hình phần tử ký sinh PCB ở tần số cao.

Hiệu ứng điện dung ký sinh là một vấn đề đáng quan tâm trong bảng mạch tần số cao. Trong khi hoạt động ở tần số thấp, các yếu tố ký sinh có thể bị bỏ qua vì chúng không thực sự ảnh hưởng đến chức năng của hệ thống. Mọi pad linh kiện trong bảng mạch đều có điện dung ký sinh và mọi trace đều có điện cảm ký sinh. Các pad cũng bổ sung khả năng kháng ký sinh của chúng để kích thích sự thất thoát IR. Điện dung ký sinh có thể tồn tại giữa các vật dẫn trên PCB, bảng mạch trần, PCBA, bảng mạch lắp ráp và trong các gói linh kiện, đặc biệt là các linh kiện dán (SMD).

Vì các bản tụ điện bên trong có sự chênh lệch điện thế, nên có khả năng xảy ra dòng điện. Không quan trọng liệu điện tích có được lưu giữa các bản tụ điện hay không; dòng điện sẽ không chạy cho đến khi có sự khác biệt điện áp. Ngay khi sự chênh lệch điện áp này tăng lên, có thể quan sát thấy sự giảm tương ứng của dòng điện tử đối với tải đối với đường tín hiệu mong muốn, tác động tiêu cực đến tính toàn vẹn của tín hiệu.

Sự khác nhau giữa điện dung tạp tán và điện dung ký sinh?

Thuật ngữ điện dung tạp tán thường được sử dụng thay thế cho điện dung ký sinh. Tuy nhiên, điện dung ký sinh giải thích rằng nó sẽ cản trở hoạt động của mạch, trong khi điện dung tạp tán giải thích cách điện dung không mong muốn được đưa vào.

Điện dung tạp tán là gì?

Điện dung tạp tán không phải lúc nào cũng được cảm ứng do điện dung ảo hình thành giữa hai dây dẫn PCB mà còn do tác động của môi trường xung quanh. Do đó, nó được gọi là điện dung tạp tán.

Điện trở ký sinh trong PCB là gì?

Điện trở ký sinh tồn tại hàng loạt dọc theo các trace hoặc như một shunt giữa các phần tử dẫn điện.

Điện cảm ký sinh trong PCB là gì?

Điện cảm ký sinh tồn tại dọc theo một trace và thể hiện hành vi lưu trữ và tiêu tán năng lượng điện, giống như một cuộn cảm thực tế. Tất cả các dây dẫn đều có tính cảm ứng và ở tần số cao, thậm chí độ tự cảm của các đoạn dây ngắn của các trace PCB có thể rất quan trọng.

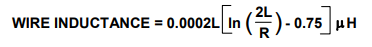

Trong đó R là bán kính dây và L là chiều dài.

LÀM THẾ NÀO ĐỂ tính ĐIỆN CẢM CỦA MỘT TRACE PCB?

Điện cảm trace tăng theo chiều dài trace và sự thiếu mặt phẳng ground plane.

Trong đó W là chiều rộng trace, L là chiều dài trace và H là độ dày trace.

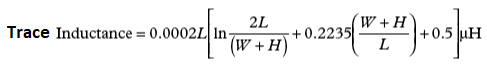

Ví dụ: một trace 2.54cm ở đầu vào không đảo của op-amp tốc độ cao sẽ dẫn đến độ tự cảm 29nH. Và điều này là đủ để bắt đầu dao động mức thấp. Điện cảm tạp tán có thể được giảm bớt bằng cách sử dụng một mặt phẳng ground plane.

Điện cảm tạp tán dẫn đến dao động mức thấp ở đầu ra op-amp.

Nguyên nhân gây ra điện dung ký sinh?

Ở tần số cao, dòng điện trong bảng mạch bị ảnh hưởng bởi điện dung ký sinh. Vì tụ điện có xu hướng trở thành vật dẫn khi tần số tăng. Lưu ý rằng khi tần số tăng lên, tụ điện sẽ hoạt động như một điện trở có giá trị rất nhỏ (tiếp cận ngắn mạch), dẫn đến dòng điện quá mức.

Zc = 1/2πfc; fc = 1 / ωc do đó, khi tần số tăng, Zc cũng tăng.

Điện dung ký sinh có thể khiến bạn ớn lạnh khi hoạt động ở tần số cao vì tụ điện hoạt động giống như một sợi dây dẫn ở tần số vô hạn. Đây là lý do tại sao nó có thể vô tình kết nối mặt phẳng tham chiếu của bất kỳ PCB nào với khung máy chassis.

Các hiệu ứng điện dung ký sinh có thể là nhiễu xuyên âm và nhiễu, phản hồi không mong muốn từ đầu ra và sự hình thành các mạch cộng hưởng. Vì vậy, điều cần thiết là phải chú ý đến thiết kế PCB tổng thể, đặc biệt là layout. Một layout tốt cần hết sức lưu ý khi đặt vật dẫn điện cạnh một vật dẫn điện khác.

Các phần tử ký sinh bao gồm các cuộn cảm được hình thành bởi các chân linh kiện, các trace dài, pad nối đất, pad linh kiện tới mặt phẳng plane nguồn, pad tới tụ điện, bao gồm tương tác với via v.v. Hiểu các phần tử ký sinh là vật ký sinh, là mối đe dọa đối với hiệu suất mạch của bạn. Không mong muốn và không thể tránh khỏi nhưng đồng thời có thể kiểm soát được.

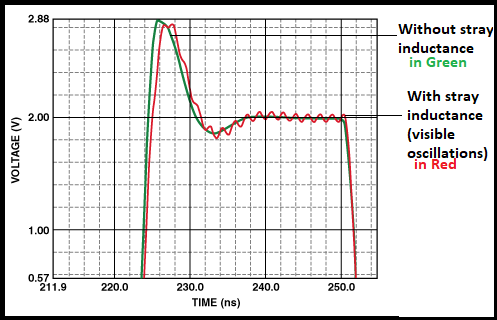

Hãy để chúng tôi lấy một ví dụ về một giản đồ điển hình của một op-amp không đảo (hình a). Kiểm tra hình b với các yếu tố ký sinh:

Sơ đồ của một op-amp không đảo với các phần tử ký sinh.

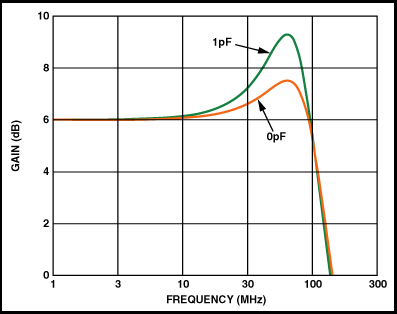

Trong các mạch tốc độ cao, một vài phần mười picofarad là đủ để ảnh hưởng đến hiệu suất của mạch. Ví dụ, 1pF của điện dung ký sinh ở đầu vào đảo có thể gây ra 2dB cực đại trong miền tần số. Và nếu nó lớn hơn 1pF, nó có thể gây ra sự mất ổn định và dao động.

Điện dung ký sinh ở đầu vào op-amp đảo.

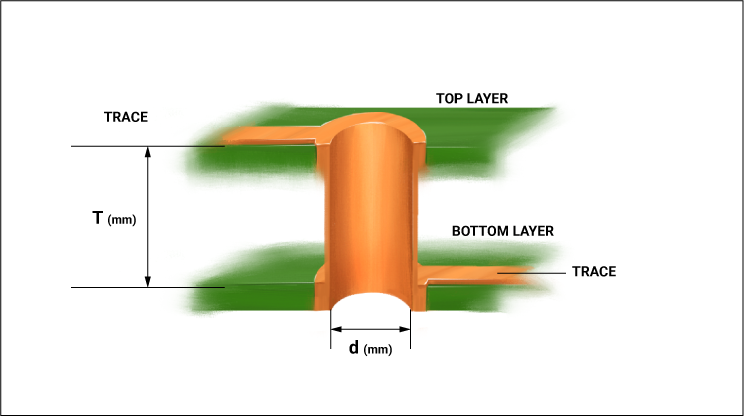

Via cũng hoạt động như các yếu tố ký sinh. Chúng bao gồm cả điện dung và điện cảm.

Via là thành phần có điện dung và điện cảm ký sinh.

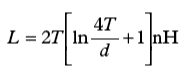

Độ tự cảm ký sinh của một via được cho bởi:

Trong đó T là độ dày của chất điện môi và d là đường kính của qua tính bằng cms.

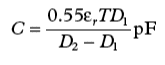

Điện dung ký sinh của một via được cho bởi:

Trong đó εr là độ từ thẩm tương đối của vật liệu mạch, T là độ dày của mạch, D1 là đường kính của tấm đệm bao quanh via và D2 là đường kính của via thủy trên mặt phẳng đất. Đọc bài đăng của chúng tôi về cách chọn vật liệu PCB và các tấm để chế tạo.

Hãy nhớ rằng via cảm ứng kết hợp với điện dung ký sinh có thể tạo thành mạch cộng hưởng. Độ tự cảm của một via đủ nhỏ để các cộng hưởng này nằm trong dải GHz, nhưng cuộn cảm mắc nối tiếp, làm giảm tần số cộng hưởng. Không đặt một số via trên một trace quan trọng của một mạch tốc độ cao. Một mối quan tâm khác là via tạo ra các lỗ trên mặt phẳng mặt đất, tạo ra các vòng lặp trên mặt đất. Chúng nên được tránh. Layout tương tự tốt nhất phải định tuyến tất cả các trace tín hiệu trên lớp trên cùng của PCB.

Giảm điện dung ký sinh trong bố trí PCB

Tụ điện chặn tín hiệu tần số thấp và DC và truyền tín hiệu tần số cao trong các mạch điện tử. Đặc tính này của tụ điện để truyền tín hiệu tần số cao (tốc độ phóng điện của tụ điện là một lý do khác khiến chúng được sử dụng thay cho pin chậm hơn nhiều) là nguyên nhân gây ra sự cố điện dung tạp tán trong mạch tốc độ cao. Đối với dây dẫn, điện dung tạp tán có thể tạo ra EMI hoặc nhiễu sẽ truyền xuống dây và cáp hoặc truyền sang các trace lân cận gần đó. Thông thường, việc loại bỏ điện dung tạp tán là không thể. Tuy nhiên, vẫn có những cách hiệu quả để giảm thiểu nó ở cấp độ bố trí PCB.

- Tránh định tuyến song song: Với định tuyến song song, giữa hai kim loại có diện tích cực đại nên giữa chúng có điện dung cực đại.

- Moating: Power plane được coi là AC ground và hoạt động giống hệt như ground plane. Vì vậy, việc loại bỏ các mặt phẳng power plane cũng quan trọng như loại bỏ các mặt phẳng ground plane khỏi vùng lân cận của dây dẫn. Kỹ thuật này được gọi là Moating.

- Sử dụng lá chắn Faraday hoặc vòng bảo vệ: Lá chắn Faraday hoạt động như một tấm che chắn và nó được đặt giữa hai trace để giảm thiểu các hiệu ứng điện dung.

- Tăng không gian giữa các trace liền kề: Điện dung giảm dần theo khoảng cách. Sử dụng quy tắc 2W hoặc 3W.

- Tránh sử dụng quá nhiều via: Via cần thiết để kết nối các lớp khác nhau của PCB. Nhưng việc sử dụng chúng quá nhiều có thể làm tăng điện dung. Để giảm khớp nối PTH, tốt hơn là giảm các annular ring xung quanh via trên các lớp không có kết nối. Do đó, giảm thiểu số lượng via từ các thành phần, như BGA.

- Tách thành phần cẩn thận: Tách các thành phần và dây dẫn, vòng bảo vệ, mặt phẳng nguồn, mặt phẳng nối đất, che chắn giữa đầu ra và đầu vào một cách cẩn thận và kết thúc đường truyền thích hợp là điều cần thiết để giảm điện dung ký sinh không mong muốn.

- Sử dụng vật liệu điện môi có điện trở thấp: Giữ cho tất cả các biến số khác không đổi, vật liệu điện môi có điện trở cao hơn tạo ra điện dung sai lệch lớn hơn, trong khi điện dung thấp hơn tạo ra điện dung ít tạp tán hơn.

- Lớp tín hiệu nên được kẹp giữa hai mặt phẳng ground plane hoặc giữa mặt phẳng ground plane hoặc mặt phẳng power plane: Trong bảng mạch 4 lớp, bạn có thể đặt mặt phẳng power plane ở lớp dưới cùng và định tuyến một số trace nhạy cảm giữa mặt phẳng power plane và ground plane. Điều này sẽ ngăn EMI từ các tín hiệu trong một lớp gây nhiễu cho các tín hiệu ở lớp khác.

- Xác định độ dày layer phù hợp: Các lớp mỏng hơn sẽ làm giảm diện tích vòng lặp và độ tự cảm ký sinh, nhưng nó sẽ làm tăng điện dung ký sinh. Bạn có thể sử dụng các công cụ mô phỏng với các stackup khác nhau để xác định độ dày layer phù hợp.

- Kết hợp trở kháng (Impedance matching): Trong các ứng dụng kỹ thuật số tốc độ cao, một số đường dữ liệu chạy ở tốc độ hàng chục Gbps, dẫn đến sự không phù hợp trở kháng do điện dung và điện cảm ký sinh. Bất kỳ sự không khớp nào do ký sinh gây ra sẽ tạo ra phản xạ ở đâu đó trên đường truyền, cuối cùng làm tăng timing jitter và bit error rates. Trở kháng phải được kết hợp trên toàn bộ các đường tín hiệu mang dữ liệu tốc độ cao.

Đo điện dung ký sinh bằng TDR

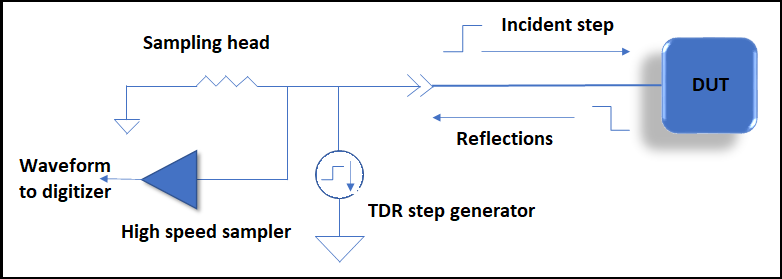

Lợi ích của việc sử dụng máy đo phản xạ miền thời gian (TDR) để đo điện cảm hoặc điện dung khi có sẵn một số máy đo LCR có độ phân giải tuyệt vời? Câu trả lời là TDR hỗ trợ các phép đo trên các thiết bị và cấu trúc khi chúng tồn tại trong mạch. Trong khi đo các yếu tố ký sinh, môi trường xung quanh của thiết bị có thể ảnh hưởng đến đại lượng cần đo. Đối với các phép đo hợp lệ, điều quan trọng là phải thực hiện các phép đo trên thiết bị vì nó tồn tại trong mạch.

Sơ đồ khối kiểm tra TDR

Sơ đồ khối kiểm tra TDR

Ngoài ra, khi đo ảnh hưởng của các thiết bị hoặc cấu trúc trong hệ thống có chứa đường truyền, TDR cho phép các phép đo riêng biệt về đặc tính đường truyền và đặc tính của thiết bị mà không cần phân tách vật lý bất kỳ thứ gì trong mạch. Cho phép chúng tôi giải thích cách TDR đo các đại lượng khó đo bằng máy đo LCR.

Ví dụ: Chúng ta hãy lấy một PCB có một trace dài và hẹp trên mặt phẳng đất, tạo thành một đường microstrip. Tại một số thời điểm, trace đi từ trên cùng của PCB xuống dưới cùng thông qua một via, v.v. Bất cứ nơi nào đường ống đi qua mặt phẳng mặt đất, nó có một lỗ nhỏ. Bây giờ, giả sử rằng via thêm điện dung vào mặt đất. Ở đây, nó sẽ là một điện dung rời rạc nối đất giữa đường truyền trên và dưới. Chúng ta đang giả định các đặc tính của đường dây tải điện và chúng ta cần đo điện dung nối đất giữa hai đường dây tải điện.

Máy đo LCR đo tổng điện dung giữa cấu trúc trace-via-trace và mặt đất. Nhưng không thể đo thông qua điện dung và điện dung trace một cách riêng biệt. Đối với các phép đo điện dung riêng biệt, các trace được xóa khỏi bảng mạch. Bằng cách này, có thể đo điện dung giữa via và đất. Và rõ ràng, giá trị điện dung này không thể được coi là chính xác đối với mô hình vì không bao gồm trace.

Mặt khác, TDR kích hoạt một sóng bước trên trace PCB và quan sát dạng sóng phản xạ từ sự gián đoạn. Lượng điện dung ‘dư thừa’ gây ra bởi qua có thể được tính bằng cách tích phân và chia tỷ lệ dạng sóng phản xạ. Phương pháp này cung cấp giá trị điện dung chính xác cho mô hình.

Sự không phù hợp giữa hai phép đo tồn tại do đồng hồ LCR đo tổng điện dung của qua trong khi TDR đo điện dung dư thừa của qua. Nếu độ tự cảm nối tiếp của mạch qua bằng không, thì tổng điện dung của nó sẽ được coi là giống như điện dung dư thừa của nó. Vì điện cảm nối tiếp của qua không bằng 0, nên phải xem xét mô hình hoàn chỉnh của qua, bao gồm cả điện cảm nối tiếp và điện dung shunt của nó. Xem xét via là điện dung, bây giờ mô hình có thể được đơn giản hóa bằng cách loại bỏ điện cảm nối tiếp và chỉ bao gồm điện dung dư thừa thay cho điện dung tổng. Điện dung dư được đo bằng TDR là giá trị chính xác cho mô hình. Cấu trúc theo dõi qua trace được mô hình hóa trước tiên để dự đoán ảnh hưởng của trace đối với các tín hiệu lan truyền dọc theo trace. TDR truyền một xung đầu vào dọc theo trace để thực hiện phép đo. Bằng cách này, TDR cung cấp một phép đo trực tiếp của đại lượng chưa biết.

Thật không may, không thể loại bỏ hoàn toàn các yếu tố ký sinh. Tuy nhiên, có một số lựa chọn bố trí PCB đơn giản mà bạn có thể thực hiện để giảm hiệu ứng điện dung ký sinh. Lựa chọn các thành phần phù hợp cũng có thể ngăn ngừa các vấn đề tín hiệu phát sinh từ điện dung và điện cảm ký sinh. Các quyết định thiết kế và sản xuất chính xác có thể kiểm soát những ký sinh trùng này.

Tham khảo: https://www.protoexpress.com/blog/how-to-reduce-parasitic-capacitance-pcb-layout/