Điều gì về một giao tiếp được kiểm soát trở kháng như USB? Nhu cầu kiểm soát trở kháng và biết khi nào nó có thể bị vi phạm, là điểm chính để định tuyến một thứ gì đó như USB trên PCB 2 lớp. Trong bài viết này, tôi sẽ chỉ cho bạn cách bạn nên định tuyến một giao thức tốc độ cao như USB. Cụ thể, chúng ta sẽ xem xét các quy tắc thiết kế quan trọng cần thiết để định tuyến bo mạch, đặc biệt là giới hạn độ dài mà chúng ta có thể chấp nhận đối với các trace mang dữ liệu USB.

Bắt đầu: Yêu cầu định tuyến tốc độ cao USB 2.0

Trong bài viết trước về định tuyến PCB 2 lớp, chúng ta đã xem xét một quy trình để xác định độ dài đường thẳng dài nhất có thể mà bạn có thể sử dụng trong thiết kế của mình mà không cần áp dụng kết hợp trở kháng. Chúng ta nhận thấy rằng giới hạn chiều dài phụ thuộc vào mức độ sai lệch trở kháng đầu vào mà bạn có thể chịu được dọc theo chiều dài của đường truyền. Đặc biệt, tùy thuộc vào việc bạn có coi 10% đến 25% khoảng cách truyền tín hiệu là yếu tố quan trọng để hạn chế độ dài trace hay không.

Đối với bản demo này, tôi muốn xem xét định tuyến USB 2.0 trên bo mạch này theo tiêu chuẩn Tốc độ cao và tôi đang tập trung vào tiêu chuẩn này vì một lý do cụ thể. USB 2.0 (High Speed) vẫn được sử dụng trong một số hệ thống vì nó cung cấp kết nối với các thiết bị cũ hơn cùng với tốc độ truyền dữ liệu nhanh và nó vẫn được sử dụng trên các nền tảng phổ biến như Arduino với cổng USB Type B.

Chỉ để minh họa hai thiết kế khả thi, tôi đã so sánh tốc độ dữ liệu và rise time của hai thông số kỹ thuật USB 2.0 (Full Speed và High Speed):

| Rise/Fall của trình điều khiển driver (tối thiểu) |

500 ps (High Speed) 4 – 20 ns (Full Speed) |

| Độ lệch cặp vi sai (tối đa) | 100 ps (High Speed)

1 đến 5 ns (Full Speed) |

| Mục tiêu trở kháng | 90 Ohms vi sai |

Quy trình tôi sẽ trình bày bên dưới được thực hiện đối với tín hiệu USB 2.0 với rise time và độ lệch skew cho High Speed , nhưng bạn có thể áp dụng quy trình tương tự cho USB 3.0 hoặc bất kỳ giao tiếp tốc độ cao nào khác. Chỉ cần nhớ: định tuyến trên bảng 2 lớp không thích hợp cho mọi giao tiếp . Ví dụ: tôi không biết bất kỳ ai sẽ đề xuất định tuyến DDR4 trên bo mạch 2 lớp do giới hạn độ dài nhỏ và nhiễu bức xạ từ các tín hiệu nhanh này.

Độ dài tới hạn

Đầu tiên, chúng ta muốn biết độ dài tới hạn cho tín hiệu USB được định tuyến trên PCB 2 lớp phổ biến. Đối với lõi Dk = 4,8 của vật liệu FR4 , chúng ta sẽ có độ trễ lan truyền xấp xỉ 150 ps/inch, hoặc khoảng 6 inch/ns. Với rise time 500 ps của chúng ta cho thông số High Speed, điều này mang lại khoảng cách truyền tín hiệu là 3 inch trong rise time. Nếu chúng ta rất thận trọng và sử dụng giới hạn 10% cho độ dài tới hạn, thì độ dài tới hạn là 0,3 inch!

Cấu trúc liên kết chúng ta cần định tuyến ở đây chỉ là một đường nối tiếp với các cặp vi sai. Vì vậy, bạn có ba yếu tố:

- Linh kiện trình điều khiển hoặc bộ xử lý của bạn với giao tiếp USB

- Các điện trở termination

- Connector giữ cáp USB của bạn

Bạn có thể tự hỏi, làm thế nào nó được thực hiện trên một nền tảng như Arduino? Hãy xem hình ảnh bên dưới của Arduino Mega bạn có thể mua trên Amazon. Bộ điều khiển USB (Atmega 16U2) được đặt gần với connector cổng USB và chắc chắn là trong vòng 1 inch.

Bảng mạch ví dụ Arduino Mega. Lưu ý rằng chip điều khiển USB gần với cổng USB Type B.

Bảng mạch ví dụ Arduino Mega. Lưu ý rằng chip điều khiển USB gần với cổng USB Type B.

Bạn sẽ tìm thấy vị trí và định tuyến tương tự trên các bảng Arduino khác. Để tránh trở kháng đầu vào không khớp với connector, cáp và bộ thu, chúng ta muốn làm theo lời khuyên được hiển thị ở trên và giữ cho tuyến ngắn trên PCB 2 lớp của chúng ta. Tuy nhiên, chúng ta không cần phải quá thận trọng khi áp dụng giới hạn 10%. Thay vào đó, nếu chúng ta đi với giới hạn 25%, chúng ta sẽ có khoảng cách định tuyến thoải mái hơn nhiều là 0,75 inch, dễ quản lý hơn nhiều trên PCB 2 lớp.

Lưu ý rằng điều này dành cho thông số ở chế độ USB High Speed. Theo thông số Full Speed, chúng ta có chiều dài tới hạn 2,4 inch (giới hạn 10%) hoặc chiều dài tới hạn 6 inch (giới hạn 25%) thoải mái hơn cho rise time 4 ns.

Điện trở đầu cuối (termination)

Tiếp theo, chúng ta cần xem xét cách đầu cuối (termination) đầu ra của trình điều khiển. Vì chúng ta đang nói cụ thể về USB ở đây, hãy lưu ý rằng thông số kỹ thuật USB 2.0 yêu cầu một số điện trở đầu cuối (termination) trên đường D + và D- gần connector để đảm bảo hòa hợp trở kháng. Chúng có thể được tích hợp vào bộ thu phát USB USB transceiver trên chip hoặc chúng có thể được yêu cầu như một linh kiện điện trở bên ngoài. Các giá trị điển hình là 15 Ohms, 22 Ohms hoặc 45 Ohms, mặc dù có thể sử dụng các giá trị khác; đảm bảo kiểm tra biểu dữ liệu cho thành phần của bạn để xem việc chấm dứt nào là cần thiết. Ví dụ, bộ điều khiển Hub USB TUSB2077APTR sử dụng điện trở đầu cuối 27 Ohm. Đảm bảo kiểm tra biểu dữ liệu để kiểm tra xem bạn có cần các điện trở bên ngoài này hay không.

Skew khác biệt

Với giới hạn lệch 100 ps trong tiêu chuẩn Tốc độ cao, giờ đây chúng ta có thể tính toán độ lệch chiều dài cho phép giữa hai mặt của cặp vi sai (tín hiệu D + và D-). Lấy ước tính độ trễ lan truyền gần đúng 6 ns / inch cho định tuyến lớp bề mặt và nhân với giới hạn xiên, chúng ta nhận được chênh lệch độ dài trace 0,6 inch. Điều này là rất lớn! Chúng ta có rất nhiều quyền tự do để cho phép một số đối sánh độ dài trace. Tuy nhiên, có một điểm quan trọng ở đây: điều này bao gồm toàn bộ chiều dài của kết nối (bo mạch của bạn + cáp + bo mạch nhận). Do đó, để an toàn, bạn hãy cố gắng hạn chế xiên nhất có thể bằng cách định tuyến các cặp lại với nhauvà thực thi đối sánh độ dài trên bảng. Điều này khá dễ dàng vì chip điều khiển USB nói chung sẽ đặt tín hiệu D + và D- trên cùng một cạnh của chip.

Kiểu định tuyến của bạn: Các cặp vi sai được ghép nối hoặc các bước vi sai lệch đồng phương

Như tôi đã chỉ ra trong blog trước , bạn không thể sử dụng chiều rộng trace tương ứng với trở kháng đặc trưng trong USB 2.0 Tốc độ cao mà vẫn đáp ứng thông số trở kháng. Hãy nhớ rằng, chiều rộng trace trên PCB có độ dày tiêu chuẩn với hai lớp là khoảng 110 mils đối với Dk – 4,8. Làm thế nào chúng ta có thể đạt được thông số trở kháng của cặp vi sai trong USB 2.0 tốc độ cao với độ rộng trace đó?

Trong thực tế, chúng ta không cần sử dụng chiều rộng trace đó do cách các trace trong các cặp vi sai sẽ ghép nối với nhau. Nếu bạn sử dụng máy tính xếp chồng lớp của mình với bảng 2 lớp dày để tính toán trở kháng vi sai cho microstrips, bạn sẽ thấy rằng chiều rộng trace thực tế cần thiết nhỏ hơn nhiều và là một hàm của khoảng cách. Đối với các dòng microstrip ví dụ của chúng ta trên PCB 2 lớp, Trình quản lý stack up trong Altium Designer cho chúng ta biết rằng chiều rộng trace là khoảng 16 mils cho khoảng cách 5 mils.

Kết quả trở kháng microstrip vi sai trong Trình quản lý Stackup của Nhà thiết kế Altium .

Kết quả trở kháng microstrip vi sai trong Trình quản lý Stackup của Nhà thiết kế Altium .

Bạn có thể sử dụng các trace nhỏ hơn với các microstrips vi sai này, nhưng bạn sẽ cần sử dụng một khoảng cách nhỏ hơn. Trong thiết kế này, chúng ta đã gần đạt đến giới hạn của khoảng cách từ trace cho quá trình khắc, vì vậy việc giữ khoảng cách 5 mil giữa các trace là không sao vì chúng ta đang đạt thông số kỹ thuật một đầu và thông số kỹ thuật khác biệt với các độ rộng trace này. Làm thế nào để chúng ta biết chúng ta đang đạt đến phần đầu cuối (termination) duy nhất của thông số kỹ thuật? Điều này là do: độ rộng trace cho ở trên là dành cho trở kháng chế độ lẻ của một trace, không phải trở kháng đặc trưng! Đây là lý do tại sao bạn cần phải gắn bó với giá trị cụ thể này cho độ rộng trace và không sử dụng giá trị trở kháng đặc trưng cho một microstrip riêng lẻ.

Có một giải pháp thay thế mà chúng ta không thảo luận: sử dụng các cặp vi sai vi mạch đồng phẳng coplanar. Bằng cách chạy đổ đất lên đến microstrips trên lớp bề mặt và bằng cách đặt đổ đất bên dưới tín hiệu ở lớp dưới cùng, bạn có thể đạt được trở kháng vi sai 90 Ohms với khoảng cách rộng 9,5 mil, khoảng cách trace 5 mil và khoảng cách so với mặt đất 5 mil . Chúng ta có thể thấy từ các giá trị bên dưới rằng chúng ta đạt được mức trở kháng 90 Ohm cần thiết trong thông số kỹ thuật USB 2.0 với các giá trị này.

Kết quả trở kháng vi sai đồng pha trong Trình quản lý stack up của Nhà thiết kế Altium .

Kết quả trở kháng vi sai đồng pha trong Trình quản lý stack up của Nhà thiết kế Altium .

Với cách sắp xếp này, chúng ta sẽ không phải lo lắng nhiều về vấn đề chiều dài quan trọng và vấn đề chiều rộng trace trong bảng 2 lớp. Tuy nhiên, bạn cần lưu ý rằng độ rộng và khoảng cách này phải được duy trì trong suốt chiều dài của tuyến đường. Định tuyến USB coi các trace là các trace một đầu riêng lẻ chỉ tình cờ mang tín hiệu khác biệt, vì vậy bạn có thể định tuyến chúng một cách riêng biệt.

Bên trong PCB Layout

Cấu trúc định tuyến khá đơn giản: định tuyến từ chip USB đến các điện trở đầu cuối (termination) / pull-up/pull-down và sau đó đến connector, tất cả đều là các cặp vi sai. Hình ảnh bên dưới cho thấy cấu trúc liên kết định tuyến mức cao với các điện trở kéo lên và kéo xuống. Một số tụ điện cũng được yêu cầu theo tiêu chuẩn USB 2.0 như hình dưới đây.

Cấu trúc liên kết định tuyến để định tuyến USB 2.0 full-speed và high-speed.

Cấu trúc liên kết định tuyến để định tuyến USB 2.0 full-speed và high-speed.

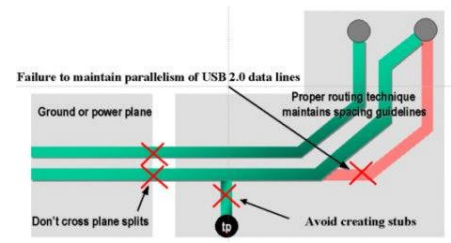

Định tuyến khá đơn giản: tuân theo các thông lệ định tuyến theo cặp vi sai tiêu chuẩn giữa mỗi phần của hệ thống và bạn sẽ không gặp vấn đề với việc đăng ký tín hiệu hoặc khớp trở kháng. Giữ các tuyến ngắn với các kết nối trực tiếp đi ra khỏi các đường cặp vi sai để tạo kết nối với GND / VCC cho các điện trở kéo xuống và kéo lên. Đảm bảo kiểm tra mạch ứng dụng cho thiết bị của bạn trong bảng dữ liệu vì các dòng D + / D- có thể có thêm tụ điện bên ngoài trên thiết bị; bạn sẽ thấy điều này trên thiết bị TUSB2077A mà tôi đã trích dẫn ở trên.

Chúng ta sẽ đưa ra một ví dụ thực tế về layout PCB trong một blog sắp tới. Hiện tại, hãy tự mình thử điều này và xem liệu bạn có thể định tuyến thiết kế hay không.

Tóm lược

Trong blog này và bài đăng trên blog trước của chúng ta, chúng ta đã xem xét một số quy tắc định tuyến quan trọng cần tuân theo khi thiết lập và định tuyến giao tiếp tốc độ cao như USB trên PCB 2 lớp. Dưới đây là nguyên tắc định tuyến cuối cùng của chúng ta:

- Giữ độ dài trace nhỏ hơn 0,75 inch mà không cần kiểm soát trở kháng

- Giữ cho chiều dài cặp vi sai chênh lệch độ dài trong vòng 0,6 inch

- Nếu không thể thực hiện # 1 do yêu cầu về kích thước hoặc chiều dài bo mạch, hãy sử dụng differential microstrip hoặc coplanar differential microstrip (cả hai đều có trở kháng được kiểm soát) để đạt thông số trở kháng vi sai 90 Ohm

Các nguyên tắc định tuyến được đề cập ở đây không phải lúc nào cũng đảm bảo EMC, có những khía cạnh khác của thiết kế cần xem xét, đôi khi được thực hiện kém trong PCB 2 lớp. Tuy nhiên, những hướng dẫn này chắc chắn sẽ hữu ích với EMI nếu bạn đang làm việc với thông số Full Speed. Sở thích cá nhân của tôi là sử dụng PCB 4 lớp cho các bus kỹ thuật số nối tiếp và các giao thức tốc độ cao, đặc biệt nếu bo mạch lớn hơn hoặc sắp được sản xuất với số lượng lớn.

Nếu bạn đang sử dụng USB 3.0, thì bạn có các yêu cầu nghiêm ngặt về khớp độ dài length matching do tốc độ cạnh fast edge rate nhanh và bạn nên đặt giao tiếp gần với connector như chúng ta đã thực hiện với thông số Full Speed được liệt kê ở trên.

Dịch từ: https://resources.altium.com/p/routing-requirements-usb-20-2-layer-pcb