Sử dụng bốn mẹo này để trở thành bậc thầy về thiết kế bảng mạch in kết nối mật độ cao.

Kết nối mật độ cao (High-density interconnect HDI) thể hiện sự tiên tiến của ngành công nghiệp bảng mạch in ngày nay, do nhu cầu về tính toàn vẹn của tín hiệu và bảng mạch nhỏ gọn. Nhưng bạn có thành thạo thiết kế bảng HDI như bạn nên không?

Trong loạt bài viết trước của chúng tôi khi trở thành bậc thầy về thiết kế PCB , chúng tôi đã tập trung vào việc thiết kế lắp ráp bảng mạch và đạt được thời gian đưa ra thị trường nhanh hơn. Bài viết này sẽ tập trung vào những điểm tốt hơn mà các nhà thiết kế phải biết để sử dụng thành thạo các bo mạch HDI.

PCB kết nối mật độ cao (HDI) là gì?

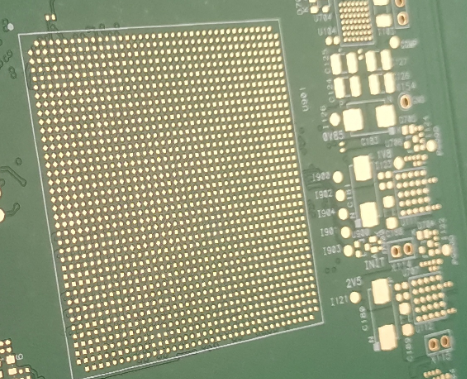

Bảng HDI có mật độ dây cao hơn trên một đơn vị diện tích bề mặt so với bảng mạch tiêu chuẩn. HDI sử dụng một số hoặc tất cả các tính năng dưới đây để giảm kích thước của bảng:

- Các line và khoảng trống space nhỏ hơn hoặc bằng 100 micromet.

- Via nhỏ hơn hoặc bằng 150 micromet.

- Các pad nhỏ hơn hoặc bằng 400 micromet.

- Mật độ pad lớn hơn 20 pad trên mỗi cm vuông.

Mật độ kết nối tăng lên cho phép nâng cao cường độ tín hiệu và cải thiện độ tin cậy. Ngoài ra, nhờ hiệu quả thiết kế và tối đa hóa không gian, bo mạch HDI có thể sản xuất các thiết bị điện tử nhỏ hơn, mạnh mẽ hơn.

Tại sao là bảng mạch HDI?

Tại sao lại có một loại công nghệ bo mạch riêng biệt được gọi là HDI? Chà, khi các đường line nhỏ hơn 65 micron (2,559 mils), khả năng khắc trace và không gian của bạn sẽ giảm đi. Bạn thực sự không thể sử dụng quy trình khắc truyền thống. Ví dụ, việc khắc điển hình trên bảng mạch tiêu chuẩn cho phép tạo ra một điện trở rất dày cùng với hình ảnh tiêu chuẩn trên máy LDI và về cơ bản bạn có nhiều không gian cho bất kỳ dung sai nào cần thiết để khắc những khoảng trống đó. Trong môi trường vi điện tử, bạn không có bất kỳ sự chậm trễ nào trong số đó. Các tính năng gần nhau đến mức các quy trình khắc truyền thống không hoạt động.

Công nghệ HDI là lựa chọn tốt nhất cho các nhà thiết kế bo mạch khi họ yêu cầu mật độ linh kiện cao hơn. Vậy điều gì làm cho HDI khác với bảng mạch tiêu chuẩn? Chủ yếu là ba điều:

- Microvia thay thế via xuyên lỗ (through-hole via) trong các khu vực mật độ linh kiện cao hơn của bảng mạch

- Các lựa chọn thay thế stack-up để chứa microvia

- Sắp xếp via để cải thiện định tuyến

# 1 Microvia thay thế via xuyên lỗ – Tại sao microvia cho HDI?

HDI sử dụng microvia thay vì via xuyên lỗ, nơi yêu cầu độ chính xác cao hơn. Microvia được khoan bằng laser có thể được sử dụng ở độ sâu lỗ khoan khoảng 100µm. Vì microvia có ống trụ dẫn điện-barrel ngắn nên chúng không gặp vấn đề với các giá trị CTE (hệ số giãn nở nhiệt) khác nhau của chất nền substrate và đồng copper. Đó là lý do tại sao microvia phù hợp hơn via xuyên lỗ.

Thực tiễn tốt nhất để thiết kế HDI hiệu quả là thay thế các via phổ biến nhất (mù, chôn lấp hoặc xuyên lỗ) bằng vi vi. Di chuyển các lớp thường được sử dụng nhất (Ví dụ: GND hoặc PWR) lên trên cùng của stack-up nếu chúng không có các linh kiện và trace trên chúng (các mặt phẳng plane GND và PWR cần phải chắc chắn và không bị vỡ). Sự sắp xếp stack-up này có thể loại bỏ via cần thiết hoặc cho phép thay thế các lỗ thông bằng các microvia. Vì các microvia không đi xuyên suốt chiều dày của bảng, điều này cung cấp nhiều không gian hơn trên các lớp khác. Do đó, phương pháp này có thể cải thiện mật độ định tuyến của lớp bên trong và giảm số lượng lớp tín hiệu.

# 2 Các lựa chọn thay thế stack-up để loại bỏ via xuyên lỗ

Các stack-up khác nhau được sử dụng trong cấu trúc HDI để giảm số lượng lỗ xuyên và số lớp bên trong. Plane đất và plane nguồn là những lớp được sử dụng nhiều nhất để khoan via. Các nhà thiết kế HDI PCB có thể giảm số lượng chồng lên bằng cách đặt các lớp này ở trên cùng của chồng lên, chẳng hạn như lớp 2 và 3. Các lớp trên cùng và dưới cùng thường được sử dụng để bố trí linh kiện.

Ba ví dụ về HDI stack-up

Các lớp điện môi mỏng nhỏ hơn 0,005 inch được sử dụng để tách các mặt phẳng plane GND và PWR. Điều này cung cấp trở kháng nguồn điện thấp và cũng cho phép sử dụng ‘skip via’ từ lớp 1 đến lớp 3.

# 3 Sắp xếp via để cải thiện định tuyến

Việc sắp xếp via hợp lý là rất quan trọng trong thiết kế bo mạch HDI. Việc sắp xếp nhằm mục đích cung cấp tính toàn vẹn của tín hiệu tốt hơn và cải thiện không gian định tuyến ở các lớp bên trong. Dưới đây là mô tả của các via stack-up:

VIA STACK-UP

Via stack-up

Các BGA Fine-pitch tạo ra một sự phức tạp cần thiết với HDI trong đó các quy tắc thiết kế được chọn để không cung cấp clearance cho các via mù so le (staggered blind via). Cần phải xếp chồng hai microvia hoặc đặt một microvia lên trên via chôn (buried via) khi tình huống này phát sinh.

CÁC BOULEVARD ĐƯỢC TẠO BỞI đặt via

Via mù được sắp xếp để tạo thành một cấu trúc boulevard. Việc hình thành boulevard có thể giảm tổng số lớp power và tăng gấp đôi không gian định tuyến.

Sắp xếp boulevard

Sắp xếp boulevard

Những cấu trúc này có thể được tạo ra bằng skip via, tích tụ nhiều hoặc nhiều lớp tuần tự và nhiều lớp via (multiple buildup, or sequentially laminated, and laminated vias). Nó cũng được sử dụng để định tuyến các tín hiệu tốc độ cao quan trọng chỉ sử dụng kết nối chéo từ ngang sang kết nối dọc của các via mù điện cảm nhỏ và thấp.

Thiết kế PCB HDI

Trong quá khứ, kết nối mật độ cao đã đi ngược lại với công nghệ bảng mạch. Và ngày nay, với rất nhiều đổi mới và đầu tư, chúng tôi có thể vượt qua ranh giới của việc chế tạo bảng mạch khi nói đến chiều rộng và không gian của trace. Vì vậy, thiết kế PCB HDI về cơ bản được xác định bởi các khoảng trống giữa các trace cũng như tất cả các đặc tính của đồng. Về vấn đề đó, chúng tôi muốn xác định HDI và vi điện tử microelectronic và cung cấp một vài gợi ý cho bạn về việc hiểu các quy tắc thiết kế và cách chúng tác động lẫn nhau để có được một thiết kế tốt.

Để hiểu rõ về kiến trúc HDI, chúng tôi có nghĩa vụ cung cấp cho bạn thông tin cơ bản. Đầu tiên, chúng tôi sẽ kiểm tra các cấu trúc stack-up có thể có và sau đó thảo luận về cách tiếp cận nhà sản xuất với ý tưởng thiết kế.

Các tiêu chuẩn IPC mà một nhà thiết kế HDI phải biết là gì?

Trước khi thảo luận chi tiết về các quy tắc thiết kế và thiết kế HDI, chúng tôi muốn bạn làm quen với các tiêu chuẩn thiết kế HDI PCB.

IPC/JPCA-2315: Hướng dẫn thiết kế cho cấu trúc kết nối mật độ cao và via.

IPC-2226: Thông số kỹ thuật tiêu chuẩn để mô tả đặc tính vật liệu, cấu thành microvia, cấu trúc kết nối và lựa chọn các quy tắc thiết kế.

IPC/JPCA-4104: Tiêu chuẩn này giúp xác định vật liệu cần thiết cho cấu trúc HDI. Tiêu chuẩn chất lượng và đặc điểm thông số kỹ thuật cho vật liệu điện môi cho cấu trúc kết nối mật độ cao.

IPC-6016: Chứa các thông số kỹ thuật chung cho chất nền mật độ cao. Tiêu chuẩn chất lượng và đặc điểm thông số kỹ thuật cho cấu trúc HDI.

Các cấu trúc HDI cơ bản

Chúng ta hãy xem xét các cấu trúc cơ bản của công nghệ HDI PCB trước khi thảo luận về các quy tắc thiết kế và các khía cạnh khác. Hai cấu trúc HDI cơ bản tồn tại là cấu trúc “buildup”/“sequential lamination” và cấu trúc “any-layer”.

Cấu trúc build-up là loại cấu trúc HDI được sử dụng phổ biến nhất. Quá trình sequential lamination được sử dụng để xây dựng cấu trúc này. Đầu tiên, core được xây dựng và dát mỏng, sau đó tiến hành khoan, mạ và lấp đầy mặt phẳng plane này. Sau quá trình này, lớp này được dát mỏng với các lớp khác, và các quá trình khoan, mạ, và lấp đầy lặp lại.

Theo tiêu chuẩn IPC 2226, cấu trúc HDI được phân thành sáu loại:

- Loại I 1 (C) 0 hoặc 1 (C) 1 : Kết cấu với cả microvia mạ và lỗ xuyên through-hole mạ được sử dụng để kết nối với nhau. Cấu trúc loại I chỉ cho phép một lớp microvia duy nhất ở một bên hoặc cả hai bên của core. Điều này được biểu diễn ở đây là 1 (C) 0 và 1 (C) 1 . Ở đây, 0, 1,… n đại diện cho số lớp microvia ở hai bên của core và (C) đại diện cho core.

- Loại II 1 (C) 0 hoặc 1 (C) 1 : Loại 2 cho phép đặt các via xuyên lỗ through-hole trong core trước khi các lớp HDI được áp dụng và có thể có các lỗ xuyên kết nối các lớp bên ngoài từ bề mặt này sang bề mặt khác. Trong trường hợp của các lớp microvia, nó tương tự như loại I.

- Loại III 2> = (C)> = 0 : Cho phép hai hoặc nhiều lớp HDI được thêm vào trên cùng của core với các via xuyên lỗ through-hole hoặc từ bề mặt này sang bề mặt khác.

- Loại IV> = 1 (P)> = 0 : P là chất nền thụ động không có chức năng nối điện. Ở đây, các microvia được sử dụng như một lớp phân phối lại trên lớp nền thụ động đã được khoan và mạ sẵn.

- Loại V không core : Cấu trúc không core sử dụng cặp lớp layer pair.

- Kết cấu loại VI : Kết cấu “Any-layer”, thay thế cho kết cấu không core bằng cách sử dụng cặp lớp layer pair.

Hãy để chúng tôi kiểm tra cấu trúc cơ bản của HDI nhiều lớp tuần tự (sequentially laminated HDI).

1 + N + 1

Trong kiểu stack-up 1 + N + 1 , ‘1’ đại diện cho một lần cán tuần tự ở hai bên của core. Một lần cán liên tiếp thêm hai lớp đồng với tổng số N + 2 lớp. Có thêm một lớp cán mỏng trên lớp trên cùng và được phép stack-up. Sự tích hợp này phù hợp với BGA có số lượng I/O thấp hơn và độ ổn định gắn kết của nó là tuyệt vời.

2 + N + 2

Bây giờ, hãy kiểm tra stack-up 2 + N + 2 được hiển thị ở trên. Cấu trúc này chứa 2 lớp kết nối mật độ cao, phù hợp với BGA với ball pitch nhỏ hơn và số lượng I / O cao hơn. Những thiết kế này sử dụng via xếp chồng hoặc so le được làm đầy bằng đồng thường được sử dụng trong các ứng dụng truyền tín hiệu mức cao.

Cấu trúc “Any-layer” là một cách tiếp cận khác được sử dụng trong thiết kế HDI PCB. Các bo mạch Any-layer là bước tiến cấp độ tiếp theo trong HDI tuân theo tiêu chuẩn HDI loại VI. Kỹ thuật Any-layer được sử dụng cho các ứng dụng kết nối mức cao vì tất cả các lớp microvia có thể được kết nối với nhau một cách tự do.

Cấu trúc Any-layer trong HDI

Cấu trúc Any-layer trong HDI

Trong phương pháp này, các lớp microvia được sử dụng như các lớp phân phối lại trong prepreg hoặc chúng ta có thể nói chúng đang trôi nổi trong các prepregs. Microvia trong một lớp được xây dựng trước tiên, sau quá trình khoan, lấp đầy, mạ, in, khắc và cán. Sau đó, các lớp khác được xếp chồng lên trên lớp hiện có theo cùng một quy trình.

Câu hỏi số một mà các nhà thiết kế thường đặt ra là… kích thước pad nào, kích thước lỗ nào và các trace và khoảng trống có thể chật chội như thế nào? Đây là những câu hỏi hay miễn là bạn đang thiết kế một bảng tương đối chuẩn. Bạn không thể chỉ nhìn vào trang khả năng sản xuất HDI PCB của chúng tôi và không hiểu cách chúng tương tác với nhau. Đối với các sản phẩm tiêu chuẩn, nó có thể hoạt động, nhưng khi bạn đi vào các bảng phức tạp hơn như HDI hoặc vi điện tử với các bộ tính năng tốt hơn, nó có thể không hoạt động.

Ví dụ về xây dựng lớp HDI

Giả sử bạn đang xây dựng HDI với các đường rất tốt và bạn sẽ làm như vậy, giả sử kiểu stack-up 2 + 4 + 2. Vì vậy, 2 + 4 + 2 về cơ bản có nghĩa là bạn sẽ có một sub-construction chôn mà chúng tôi sẽ khoan và tạo tấm. Bây giờ, nếu chúng ta phải làm các đường thẳng trên lớp 3 của sub-construction chôn, điều đó sẽ trở thành vấn đề. Các quy trình ở lớp 3, không cho phép sử dụng công nghệ đường mịn. Trong khi ở lớp 2, bạn có nhiều thời gian hơn cho các nếp nhăn của mình.

2 + 4 + 2

Bây giờ khi bạn tham gia vào bộ tính năng đó, việc thiết kế toàn bộ bảng với các kích thước tính năng đó không giống như chỉ thiết kế một phần nhỏ của bảng với các bộ tính năng đó. Nếu bạn có thể nới lỏng khoảng cách với kích thước pad lớn hơn và kích thước khoan lớn hơn ở những khu vực không dày đặc, điều đó sẽ giúp nhà sản xuất dễ dàng hơn và ít tốn kém hơn cho bạn… đặc biệt nếu bạn đang đi vào sản xuất.

Vì vậy, chúng tôi thực sự muốn đi sâu về sự khác biệt đó. Mặc dù khả năng của chúng tôi cho rằng 35 micron là trace và không gian tối thiểu, nhưng đó không phải là kích thước tính năng mà chúng tôi muốn đề xuất hoặc có thể sản xuất trên toàn bộ thiết kế.

“Mật độ kết nối tăng lên cho phép nâng cao cường độ tín hiệu.”

Trở thành bậc thầy HDI

Mật độ cao hơn có nghĩa là các nhà thiết kế HDI phải liên tục lưu ý đến layout và khoảng cách, không gian trên PCB, và các yếu tố khác. Sau đây là bốn mẹo để tránh những lỗi thiết kế bo mạch HDI thường gặp.

1. Ưu tiên không gian

Xem xét không gian trong quá trình thiết kế HDI PCB có nghĩa là nhiều hơn là ép vào càng nhiều linh kiện càng tốt. Đầu tiên, các nhà thiết kế phải đảm bảo bảng mạch có thể được bảo trì đúng cách trong tương lai. Việc xác định khoảng trống giữa các linh kiện cụ thể và chọn thêm một phòng là một yêu cầu. Điều này cũng có thể làm cho mọi thứ đơn giản hơn trong quá trình sản xuất bảng mạch. Tất cả đường kính via, đường kính pad và chiều rộng trace đều phải được tính đến trước khi bắt đầu thực hiện. Nếu không, các bảng mạch có thể phải được thiết kế lại hoàn toàn, đòi hỏi thêm thời gian, tiền bạc và năng lượng.

2. Hiểu ý nghĩa của những via mù và chôn

Bảng HDI kết hợp các via mù và chôn để tận dụng tối đa không gian hạn chế. Via mù kết nối các lớp bên ngoài với các lớp bên trong nhưng không đi qua toàn bộ bảng mạch. Via chôn kết nối nhiều lớp bên trong nhưng không đi qua các lớp bên ngoài. Trong khi thực tế và chức năng, via mù và chôn khác với via xuyên lỗ truyền thống và ảnh hưởng lớn đến thiết kế tổng thể của bảng mạch. Các nhà thiết kế phải tập trung vào via vì chúng không chỉ ảnh hưởng đến việc xây dựng bảng mạch mà còn ảnh hưởng đến hiệu suất tín hiệu dựa trên vị trí,cách đặt của chúng.

3. Tránh các vấn đề liên quan đến chất hàn

Nếu các nhà thiết kế không cẩn thận, chất hàn có thể gây ra nhiều vấn đề. Ví dụ: via in pad có thể hút chất hàn ra khỏi các linh kiện cụ thể, dẫn đến các kết nối kém chất lượng. Một giải pháp cho vấn đề này là tránh sử dụng via in pad. Thật không may, tùy thuộc vào thiết kế bo mạch và các ứng dụng của nó, đôi khi điều này là không thể. Trong những trường hợp như vậy, việc che phủ qua pad bằng mặt nạ hàn solder mask có thể loại bỏ vấn đề. Tuy nhiên, sử dụng mặt nạ hàn có thể dẫn đến các biến chứng của riêng nó. Mặt nạ hàn với các độ mở lớn có thể cho phép một lượng đáng kể chất hàn tiếp cận với bảng mạch, dẫn đến các chốt bị tombstoning hoặc mất kết nối. Điều quan trọng là các nhà thiết kế phải theo dõi các vấn đề tiềm ẩn về mối hàn trước khi bắt đầu thiết kế.

Tham khảo bài đăng của chúng tôi về 8 lỗi phổ biến trong SMT để tìm hiểu thêm về các lỗi hàn khác nhau như lỗi tombstoning, mối nối hàn nguội cold solder joint, v.v.

4. Kết hợp các đánh giá thiết kế

Điều này áp dụng cho tất cả các dự án thiết kế bảng mạch, nhưng xứng đáng được chú trọng đặc biệt trong HDI. Có thể khó cho các nhà thiết kế rời khỏi công việc của chính họ và phát hiện ra những lỗi nhỏ. Điều này trở nên khó gấp đôi khi các nhà thiết kế đang làm việc với mật độ linh kiện cao hơn. Kết hợp lời khuyên và quan điểm từ các nhà thiết kế, kỹ thuật viên khác, v.v. là một cách chiến lược để sửa chữa những sai lầm nhỏ trước khi chúng trở thành những vấn đề lớn hơn, tốn kém hơn. Bạn có thể dễ dàng bỏ qua các bài đánh giá thiết kế để đáp ứng thời hạn chặt chẽ, nhưng cuối cùng, các bài đánh giá như vậy là cách lý tưởng để tiết kiệm thời gian và tiền bạc.

Cân nhắc thiết kế cho thiết kế HDI PCB

Bảng HDI yêu cầu một số cân nhắc thiết kế được tính đến trong quá trình thiết kế. Hãy tham khảo từng mục dưới đây:

Lựa chọn linh kiện thông minh

Thông thường, một bảng HDI chứa các linh kiện SMD (số lượng chân lớn) và BGA (≤ 0,65 mm) . Khoảng cách/kích thước pitch giữa các chân của chúng nên được chọn một cách khôn ngoan vì nó giúp xác định độ rộng trace, loại via và stack-up.

Sử dụng microvia

Sử dụng microvia hoặc công nghệ sequential build-up ( đường kính <0,15 mm ). Nó có thể giúp bạn đạt được gấp đôi số chân / diện tích so với chân xuyên lỗ. Những microvia này được sử dụng để tạo thành vùng “thoát” của các linh kiện dày đặc (I/O nhiều, micro BGA). Độ tự cảm thấp của microvia làm cho chúng phù hợp với các ứng dụng tốc độ cao, để kết nối các plane nguồn với tụ điện decoupling và những nơi cần giảm nhiễu.

Lựa chọn vật liệu

Lựa chọn vật liệu là quan trọng đối với mọi thiết kế bảng mạch. Nhưng chúng tôi phải nói rằng nó quan trọng hơn đối với bảng HDI. Mục tiêu của nhà thiết kế là chọn vật liệu phù hợp với khả năng sản xuất, đồng thời đáp ứng các yêu cầu về nhiệt độ và điện. Độ dày vật lý của vật liệu rất quan trọng khi xem xét tỷ lệ aspect ratio của microvia được mạ.

Phủ via

Phủ trong via-in-pad

Luôn lấp đầy/đậy nắp các microvia để tạo bề mặt đồng phẳng. Nó cũng cho phép dễ dàng đặt các thành phần khác ở cả hai mặt của bảng mạch. Bỏ qua điều này sẽ tạo ra bọt khí và bạn sẽ làm giảm chất lượng mối hàn.

Một lưới microvia offset

Nó cho phép thiết kế via-in-pad. Các microvia như vậy có thể được căn giữa, lệch khỏi hoặc tiếp tuyến với các pad SMD để cung cấp thêm định tuyến trace.

Offset via

Giảm đục thủng mặt phẳng plane

Khu vực đồng ground/power lớn dưới BGA cải thiện tính toàn vẹn của nguồn (PI) và EMC. Bất cứ nơi nào microvia đục thủng một mặt phẳng plane; chúng tạo ra một khoảng trống rất nhỏ với các tác động nhỏ lên SI, PI và EMC. Đục lỗ ít hơn để đạt được hiệu ứng image plane được cải thiện và hiệu quả che chắn (shielding) cao hơn.

Vấn đề Stack-up trong thiết kế HDI PCB

Các vật liệu lớp khác nhau có giá trị CTE và tốc độ hút ẩm khác nhau, điều này gây ra khả năng tách lớp delamination. Các nhà thiết kế bảng mạch có thể tránh nó bằng cách sử dụng cùng một vật liệu cho mọi lớp hoặc vật liệu có cùng giá trị CTE.

Thử nghiệm

Các phương pháp kiểm tra chức năng hoặc JTAG được sử dụng cho thiết kế HDI PCB hơn là ICT. ICT là dứt khoát nhưng cần có phân tích nút đầy đủ. Trong trường hợp BGA sử dụng microvia mù và chôn, bạn sẽ không có khả năng tiếp cận trừ khi bạn đưa chúng ra lớp ngoài (điều đó sẽ vi phạm tính toàn vẹn của tín hiệu). Nếu bạn đang sử dụng linh kiện có kiểu đóng gói small-pin, thì bạn có thể không có đủ không gian.

Quản lý nhiệt

Để cung cấp khả năng quản lý nhiệt tốt hơn cho thiết kế của bạn, hãy tham khảo IPC-2226 , liên quan đến các vấn đề về nhiệt. Các nhà thiết kế cần quan tâm hơn đến vấn đề nhiệt vì mật độ linh kiện của mạch HDI cao. Các chất điện môi mỏng hơn đi cùng với microvia là một trợ giúp cho quá trình tản nhiệt. Để tối đa hóa sự tiêu tán, hãy xem xét thêm via thermal.

Nhu cầu dây so với khả năng của chất nền

Nhu cầu dây là tổng chiều dài kết nối cần thiết để kết nối tất cả các bộ phận trong bo mạch. Khả năng của chất nền là chiều dài dây có sẵn để kết nối tất cả các linh kiện. Khả năng của chất nền phải lớn hơn nhu cầu đi dây để có đủ sức chứa đi dây để hoàn thành thiết kế với chi phí tối thiểu.

Mật độ dây của bảng mạch

Tính toán mật độ PWB để đo mức độ phức tạp của thiết kế. Lượng mật độ của bảng mạch in (Wd) được đo bằng chiều dài trung bình của trace trên inch vuông bao gồm tất cả các lớp tín hiệu.

Mật độ PWB được suy ra bằng cách giả sử trung bình có ba nút điện trên mỗi net và dây dẫn linh kiện là một nút của net.

PWB Density (Wd) =β √([Cd] )×(Cc)

=β √([(parts per sq.in.)] )×(ave.leads per part)

Ở đó:

Cd = mật độ linh kiện = Trung bình số lượng linh kiện trên mỗi inch vuông cho một thiết kế

Cc = độ phức tạp của linh kiện = Trung bình số lượng chân của mỗi linh kiện

β = Hằng số, 2.5 cho vùng tương tự (high analog )/vùng khác (discrete), 3.0 cho vùng tương tự/số và 3.5 cho vùng số/ASIC.

Tìm hiểu cách Bảng mạch HDI có thể tiết kiệm hơn

Không có cái gọi là quy tắc thiết kế chung

“Bạn chỉ phải tuân theo một quy tắc nếu bạn đang tạo ra một thứ mới“ không tuân theo quy tắc nào ”

Giả sử bạn đang kết nối một micro BGA với một trình kết nối và bạn phải định tuyến các kết nối đó. Bảng là 3 “by 3” vì vậy có rất nhiều net bạn cần kết nối trong một không gian nhỏ. Có sai khi thiết kế một bảng 4 lớp với trace 1 mil và không gian 35 micrômét chỉ để kết nối tất cả các lưới không? Vâng, đúng vậy. Vì vậy, làm thế nào để bạn phản biện điều này từ quan điểm thiết kế và sản xuất? Có 2 quyết định stack-up bạn cần thực hiện:

- Bạn sẽ thêm bao nhiêu lớp định tuyến?

- Các lớp định tuyến sẽ được kết nối như thế nào?

Bạn nên luôn cố gắng tạo một stack-up với mật độ định tuyến không gian và trace không ít hơn 3 mil. Nếu bạn cần một trace và không gian nhỏ hơn, vui lòng tham khảo ý kiến nhà sản xuất xem họ có thể xử lý trace nhỏ hơn 3 mil hay không. Các trace nhỏ hơn 3 mil sẽ tốn kém hơn nhiều. Nhưng hãy bắt đầu với con số 3 mil. Bây giờ nếu bạn làm điều đó … một cái gì đó phải cho đi. Bảng của bạn phải lớn hơn hoặc cần có nhiều lớp hơn. Vì vậy, nếu có hạn chế về không gian và bạn cần duy trì hệ số hình thức thì bạn sẽ thêm nhiều lớp định tuyến hơn, điều này hoàn toàn ổn. Bây giờ bạn sẽ kết nối các lớp định tuyến này như thế nào? Bạn sẽ kết nối với via xuyên lỗ? Về cơ bản là “phô mai Thụy Sĩ” tất cả các lớp của bạn. Hay bạn sẽ có thể kết nối với các via mù và chôn được tạo ra bởi các máy khoan laser và giải phóng rất nhiều không gian định tuyến cho bạn?

Phương án 2 là lựa chọn tốt hơn nhiều so với phương án 1

Và trong nhiều trường hợp, phương án 1 thậm chí không thể thực hiện được. Via được khoan bằng laser yêu cầu kích thước pad nhỏ hơn nhiều, giúp bạn thiết kế nhanh hơn. Và có rất nhiều nhà chế tạo PCB có thể sản xuất bảng HDI. Vì vậy, một khi bạn tìm ra mật độ định tuyến tối thiểu của mình cần thiết, sau đó bạn tìm ra stack-up của mình và nơi via của bạn sẽ bắt đầu và dừng lại. Sierra Circuits cung cấp một công cụ stack-up thực sự mang lại cho bạn một khởi đầu tốt về thế nào là thiết kế có thể sản xuất cho HDI và cấp độ công nghệ của bạn là gì đối với trace và không gian cùng với các pad và via.

Các cân nhắc khác đối với HDI là bạn chọn lớp hoàn thiện bề mặt nào, độ dày đồng bạn chọn, giá trị trở kháng và loại vật liệu. Hãy thử các công cụ HDI miễn phí của chúng tôi như Công cụ lập kế hoạch stack-up và Bộ chọn vật liệu . Để biết thêm thông tin, hãy tải xuống hướng dẫn thiết kế HDI PCB của chúng tôi.

Tham khảo:

Amit Bahl,

https://www.protoexpress.com/blog/becoming-a-pcb-master-hdi/